XC32 Compiler for PIC32M

MPLAB XC32 C/C++ Compiler User's Guide

for PIC32M MCUs

Notice to Customers

Important:

All documentation becomes dated and this manual is no exception. Microchip tools and documentation are

constantly evolving to meet customer needs, so some actual dialogs and/or tool descriptions may differ

from those in this document. Please refer to our website (www.microchip.com) to obtain the latest

documentation available.

Documents are identified with a “DS” number. This number is located on the bottom of each page, in front

of the page number. The numbering convention for the DS number is “DSXXXXXA,” where “XXXXX” is the

document number and “A” is the revision level of the document.

For the most up-to-date information on development tools, see the MPLAB

®

X IDE online help. Select the

Help menu and then Topics, to open a list of available online help files.

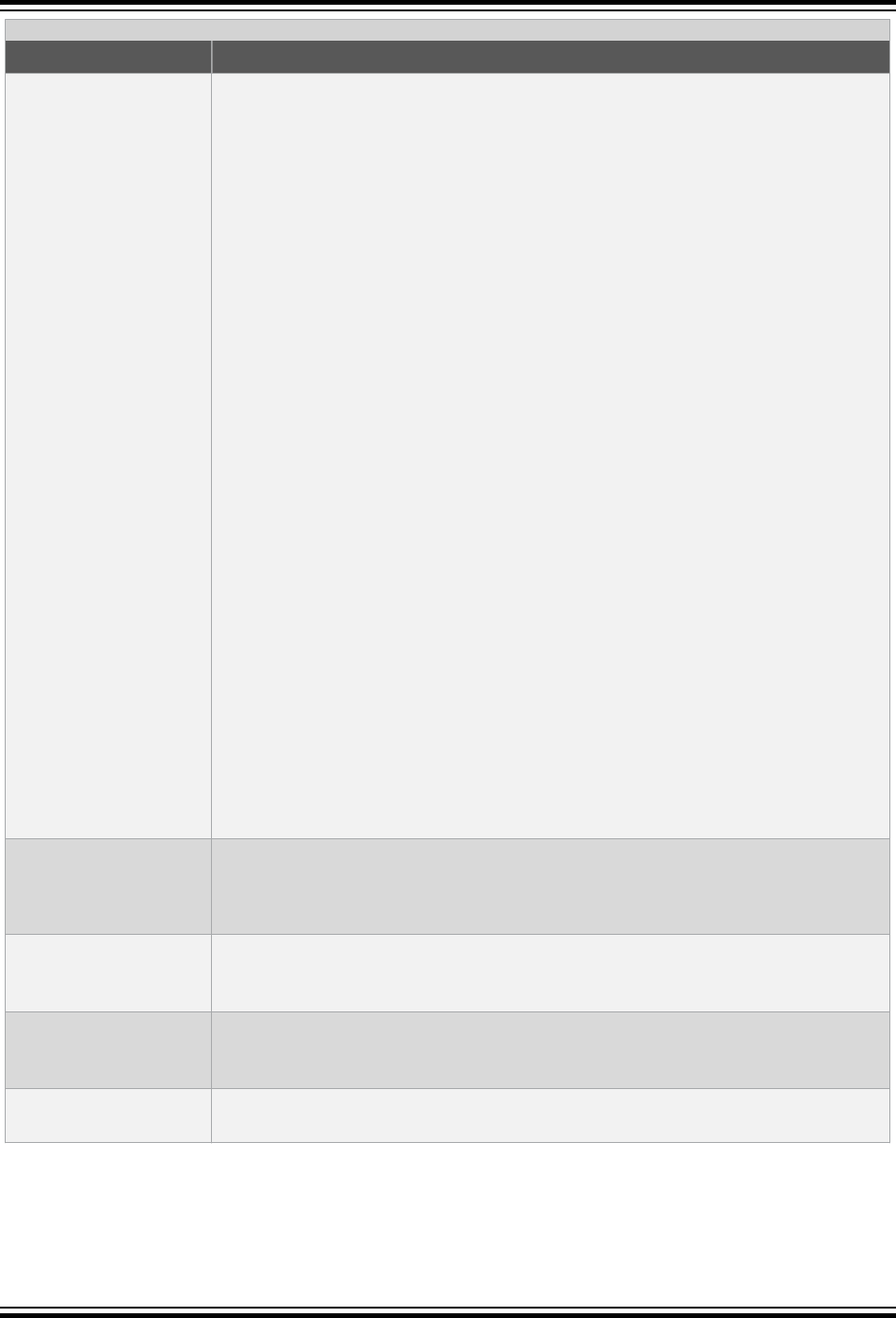

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 1

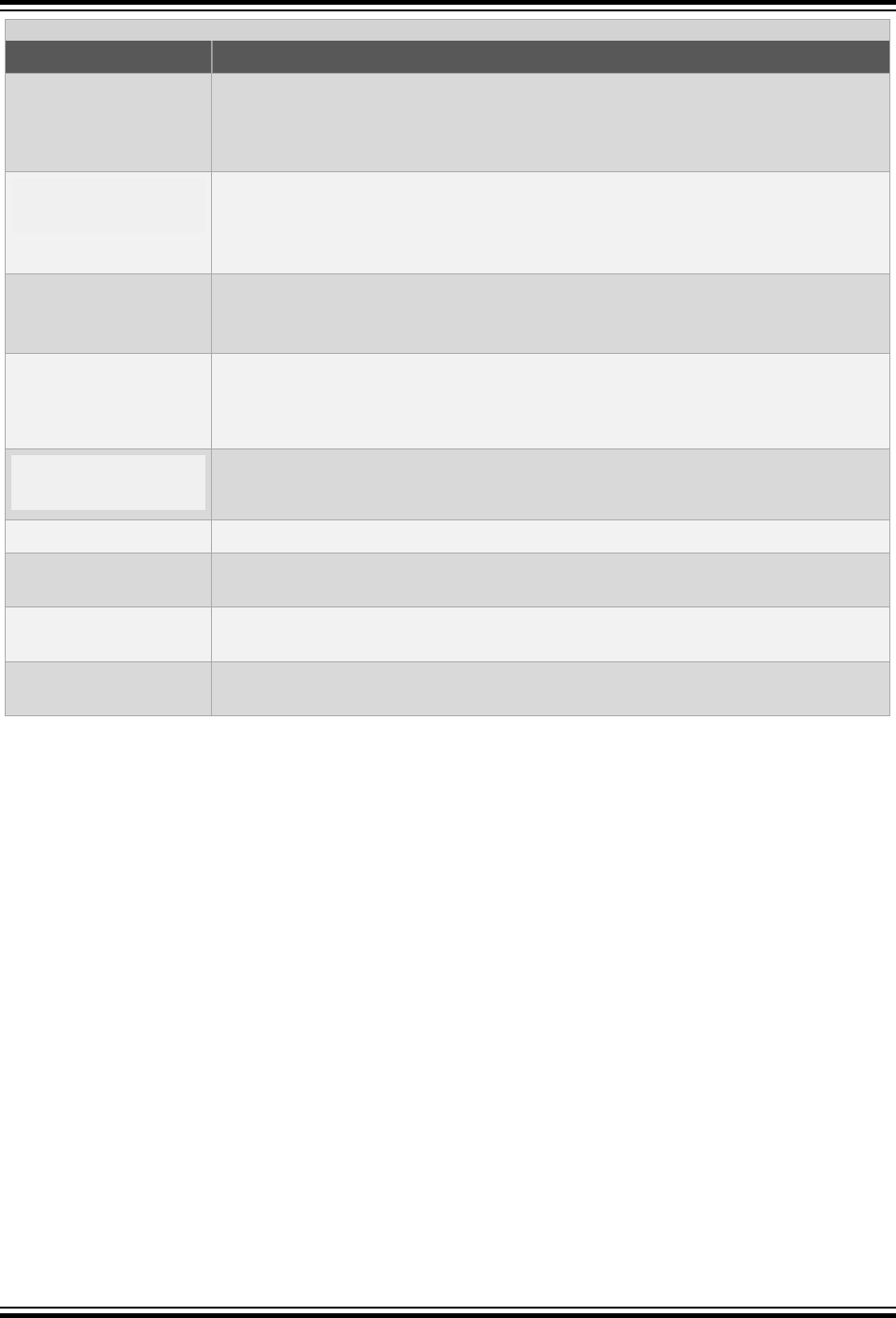

Table of Contents

Notice to Customers.......................................................................................................................................1

1. Preface....................................................................................................................................................7

1.1. Conventions Used in This Guide..................................................................................................7

1.2. Recommended Reading...............................................................................................................8

2. Compiler Overview................................................................................................................................10

2.1. Device Description..................................................................................................................... 10

2.2. Compiler Description and Documentation..................................................................................10

2.3. Compiler and Other Development Tools.....................................................................................11

3. Common C Interface............................................................................................................................. 12

3.1. Background - The Desire for Portable Code.............................................................................. 12

3.2. Using the CCI.............................................................................................................................14

3.3. ANSI Standard Refinement........................................................................................................14

3.4. ANSI Standard Extensions.........................................................................................................21

3.5. Compiler Features......................................................................................................................31

4. How To's................................................................................................................................................33

4.1. Installing and Activating the Compiler........................................................................................ 33

4.2. Invoking the Compiler.................................................................................................................34

4.3. Writing Source Code.................................................................................................................. 36

4.4. Getting My Application To Do What I Want................................................................................ 42

4.5. Understanding the Compilation Process....................................................................................45

4.6. Fixing Code That Does Not Work...............................................................................................51

5. XC32 Toolchain and MPLAB X IDE...................................................................................................... 53

5.1. MPLAB X IDE and Tools Installation.......................................................................................... 53

5.2. MPLAB X IDE Setup.................................................................................................................. 53

5.3. MPLAB X IDE Projects...............................................................................................................54

5.4. Project Setup..............................................................................................................................56

5.5. Project Example......................................................................................................................... 67

6. Command-line Driver............................................................................................................................ 69

6.1. Invoking The Compiler............................................................................................................... 69

6.2. The C Compilation Sequence.................................................................................................... 71

6.3. The C++ Compilation Sequences.............................................................................................. 73

6.4. Runtime Files............................................................................................................................. 75

6.5. Compiler Output......................................................................................................................... 78

6.6. Compiler Messages....................................................................................................................79

6.7. Driver Option Descriptions......................................................................................................... 80

7. ANSI C Standard Issues..................................................................................................................... 104

7.1. Divergence Fom the ANSI C Standard.................................................................................... 104

7.2. Extensions to the ANSI C Standard......................................................................................... 104

7.3. Implementation-Defined Behavior............................................................................................104

8. Device-Related Features.................................................................................................................... 105

XC32 Compiler for PIC32M

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 2

8.1. Device Support.........................................................................................................................105

8.2. Device Header Files.................................................................................................................105

8.3. Stack........................................................................................................................................ 105

8.4. Configuration Bit Access.......................................................................................................... 106

8.5. ID Locations............................................................................................................................. 107

8.6. Using SFRs From C Code........................................................................................................107

9. Supported Data Types and Variables..................................................................................................110

9.1. Identifiers.................................................................................................................................. 110

9.2. Data Representation.................................................................................................................110

9.3. Integer Data Types................................................................................................................... 110

9.4. Floating-Point Data Types.........................................................................................................111

9.5. Structures and Unions.............................................................................................................. 113

9.6. Pointer Types............................................................................................................................115

9.7. Complex Data Types................................................................................................................ 117

9.8. Constant Types and Formats................................................................................................... 117

9.9. Standard Type Qualifiers.......................................................................................................... 119

9.10. Compiler-Specific Qualifiers.....................................................................................................120

9.11. Variable Attributes.................................................................................................................... 120

10. Memory Allocation and Access........................................................................................................... 124

10.1. Address Spaces....................................................................................................................... 124

10.2. Variables in Data Memory........................................................................................................ 124

10.3. Auto Variable Allocation and Access........................................................................................126

10.4. Variables in Program Memory..................................................................................................127

10.5. Variable in Registers................................................................................................................ 128

10.6. Application-Defined Memory Regions......................................................................................128

10.7. Dynamic Memory Allocation.....................................................................................................131

10.8. Memory Models........................................................................................................................132

11. Fixed-Point Arithmetic Support........................................................................................................... 133

11.1. Enabling Fixed-Point Arithmetic Support..................................................................................133

11.2. Data Types............................................................................................................................... 133

11.3. External Definitions.................................................................................................................. 135

11.4. SIMD Variables.........................................................................................................................135

11.5. Accessing Elements in SIMD Variables................................................................................... 136

11.6. Array Alignment and Data Layout............................................................................................ 138

11.7. C Operators..............................................................................................................................138

11.8. Operations on SIMD Variables.................................................................................................139

11.9. DSP Built-In Functions............................................................................................................. 140

11.10. DSP Control Register............................................................................................................... 140

11.11. Using Accumulators................................................................................................................. 140

11.12. Mixed-Mode Operations........................................................................................................... 141

11.13. Auto-Vectorization to SIMD...................................................................................................... 142

11.14. FIR Filter Example Project....................................................................................................... 142

12. Operators and Statements.................................................................................................................. 145

12.1. Integral Promotion....................................................................................................................145

12.2. Type References...................................................................................................................... 146

XC32 Compiler for PIC32M

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 3

12.3. Labels as Values...................................................................................................................... 146

12.4. Conditional Operator Operands............................................................................................... 147

12.5. Case Ranges............................................................................................................................147

13. Register Usage................................................................................................................................... 149

13.1. Register Usage.........................................................................................................................149

13.2. Register Conventions...............................................................................................................149

14. Functions.............................................................................................................................................151

14.1. Writing Functions......................................................................................................................151

14.2. Function Attributes and Specifiers............................................................................................151

14.3. Allocation of Function Code..................................................................................................... 155

14.4. Changing the Default Function Allocation................................................................................ 156

14.5. Function Size Limits................................................................................................................. 156

14.6. Function Parameters................................................................................................................156

14.7. Function Return Values............................................................................................................158

14.8. Calling Functions......................................................................................................................159

14.9. Inline Functions........................................................................................................................ 159

15. Interrupts............................................................................................................................................. 161

15.1. Interrupt Operation................................................................................................................... 161

15.2. Writing an Interrupt Service Routine........................................................................................ 161

15.3. Associating a Handler Function with an Exception Vector....................................................... 165

15.4. Exception Handlers.................................................................................................................. 166

15.5. Interrupt Service Routine Context Switching............................................................................167

15.6. Latency.....................................................................................................................................168

15.7. Nesting Interrupts.....................................................................................................................168

15.8. Enabling/Disabling Interrupts................................................................................................... 168

15.9. ISR Considerations.................................................................................................................. 168

16. Main, Runtime Start-up and Reset......................................................................................................169

16.1. The Main Function....................................................................................................................169

16.2. Runtime Start-Up Code............................................................................................................169

16.3. The On Reset Routine..............................................................................................................180

17. Library Routines.................................................................................................................................. 181

17.1. Using Library Routines.............................................................................................................181

18. Mixing C/C++ and Assembly Language..............................................................................................182

18.1. Mixing Assembly Language and C Variables and Functions................................................... 182

18.2. Using Inline Assembly Language.............................................................................................184

18.3. Predefined Macros................................................................................................................... 186

19. Optimizations...................................................................................................................................... 189

20. Preprocessing..................................................................................................................................... 190

20.1. C/C++ Language Comments....................................................................................................190

20.2. Preprocessor Directives........................................................................................................... 190

20.3. Pragma Directives....................................................................................................................191

20.4. Predefined Macros................................................................................................................... 192

XC32 Compiler for PIC32M

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 4

21. Linking Programs................................................................................................................................ 196

21.1. Replacing Library Symbols.......................................................................................................196

21.2. Linker-Defined Symbols........................................................................................................... 196

21.3. Default Linker Script.................................................................................................................196

22. Embedded Compiler Compatibility Mode............................................................................................210

22.1. Compiling in Compatibility Mode..............................................................................................210

22.2. Syntax Compatibility.................................................................................................................210

22.3. Data Type................................................................................................................................. 211

22.4. Operator................................................................................................................................... 211

22.5. Extended Keywords..................................................................................................................211

22.6. Intrinsic Functions.................................................................................................................... 213

22.7. Pragmas...................................................................................................................................213

23. Implementation-Defined Behavior.......................................................................................................215

23.1. Overview.................................................................................................................................. 215

23.2. Translation................................................................................................................................215

23.3. Environment............................................................................................................................. 215

23.4. Identifiers..................................................................................................................................216

23.5. Characters................................................................................................................................216

23.6. Integers.................................................................................................................................... 217

23.7. Floating-Point........................................................................................................................... 217

23.8. Arrays and Pointers..................................................................................................................218

23.9. Hints......................................................................................................................................... 219

23.10. Structures, Unions, Enumerations, and Bit Fields....................................................................219

23.11. Qualifiers.................................................................................................................................. 220

23.12. Declarators...............................................................................................................................220

23.13. Statements...............................................................................................................................220

23.14. Pre-Processing Directives........................................................................................................220

23.15. Library Functions......................................................................................................................221

23.16. Architecture..............................................................................................................................225

24. Deprecated Features.......................................................................................................................... 226

24.1. Variables in Specified Registers...............................................................................................226

24.2. Defining Global Register Variables...........................................................................................226

24.3. Specifying Registers for Local Variables..................................................................................227

25. Built-In Functions................................................................................................................................ 228

26. Built-In Function Descriptions............................................................................................................. 229

26.1. __builtin_bcc0(rn,sel,clr).......................................................................................................... 229

26.2. __builtin_bsc0(rn,sel,set)......................................................................................................... 229

26.3. __builtin_bcsc0(rn,sel,clr,set)...................................................................................................230

26.4. __builtin_clz(x)......................................................................................................................... 230

26.5. __builtin_ctz(x)......................................................................................................................... 231

26.6. __builtin_mips_cache(op,addr)................................................................................................ 231

26.7. __builtin_mxc0(rn,sel,val).........................................................................................................232

26.8. __builtin_set_isr_state(unsigned int)........................................................................................232

26.9. __builtin_software_breakpoint(void).........................................................................................232

XC32 Compiler for PIC32M

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 5

26.10. unsigned long__builtin_section_begin(quoted-section-name).................................................233

26.11. unsigned long __builtin_section_end(quoted-section-name)................................................... 233

26.12. unsigned long __builtin_section_size(quoted-section-name).................................................. 234

26.13. unsigned int __builtin_get_isr_state(void)................................................................................234

27. Built-In DSP Functions........................................................................................................................ 236

28. ASCII Character Set............................................................................................................................242

29. Document Revision History.................................................................................................................243

The Microchip Website...............................................................................................................................244

Product Change Notification Service..........................................................................................................244

Customer Support...................................................................................................................................... 244

Microchip Devices Code Protection Feature.............................................................................................. 244

Legal Notice............................................................................................................................................... 244

Trademarks................................................................................................................................................ 245

Quality Management System..................................................................................................................... 245

Worldwide Sales and Service.....................................................................................................................246

XC32 Compiler for PIC32M

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 6

1. Preface

MPLAB

®

XC32 C/C++ Compiler for PICM MCUs documentation and support information is discussed in this section.

1.1 Conventions Used in This Guide

The following conventions may appear in this documentation:

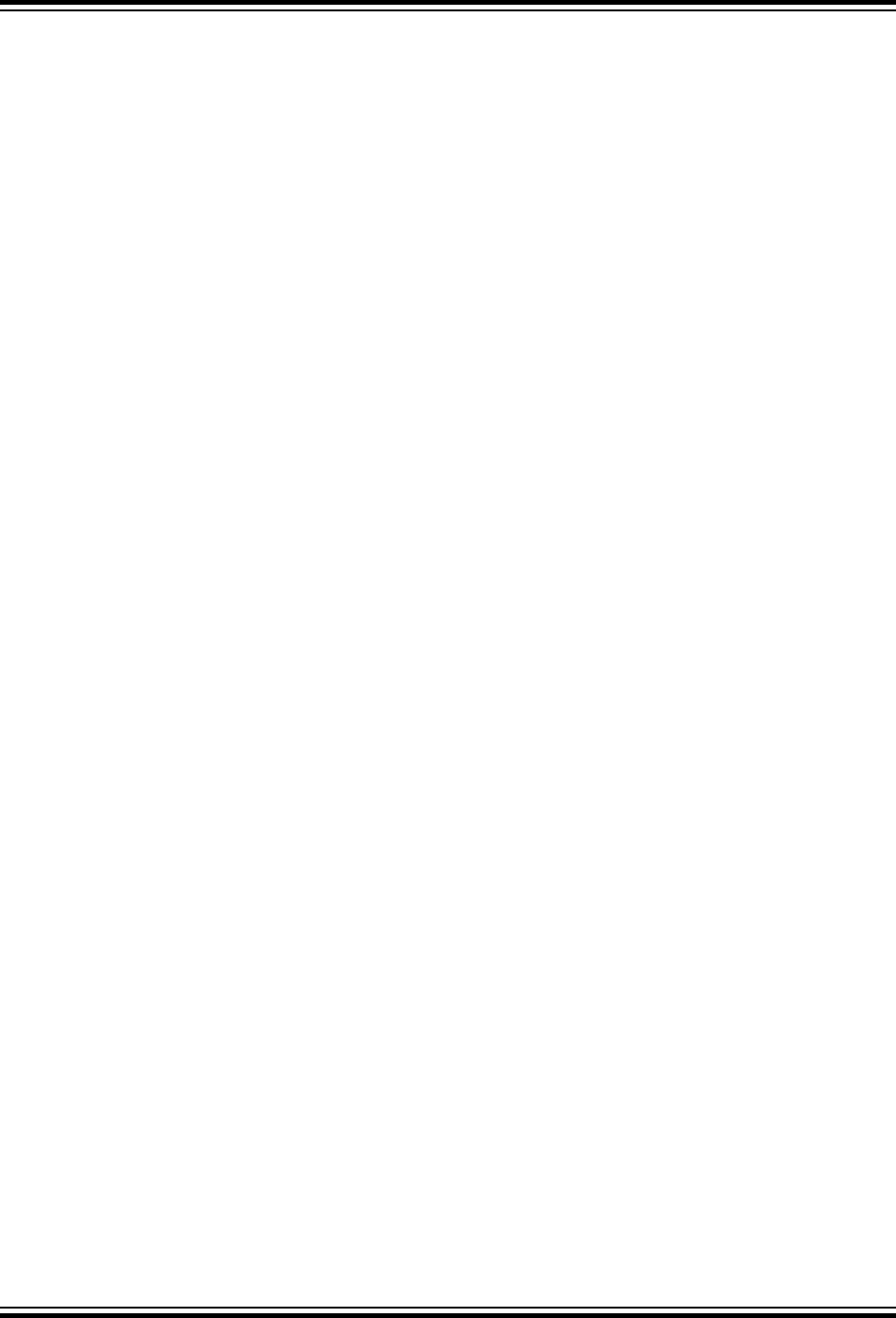

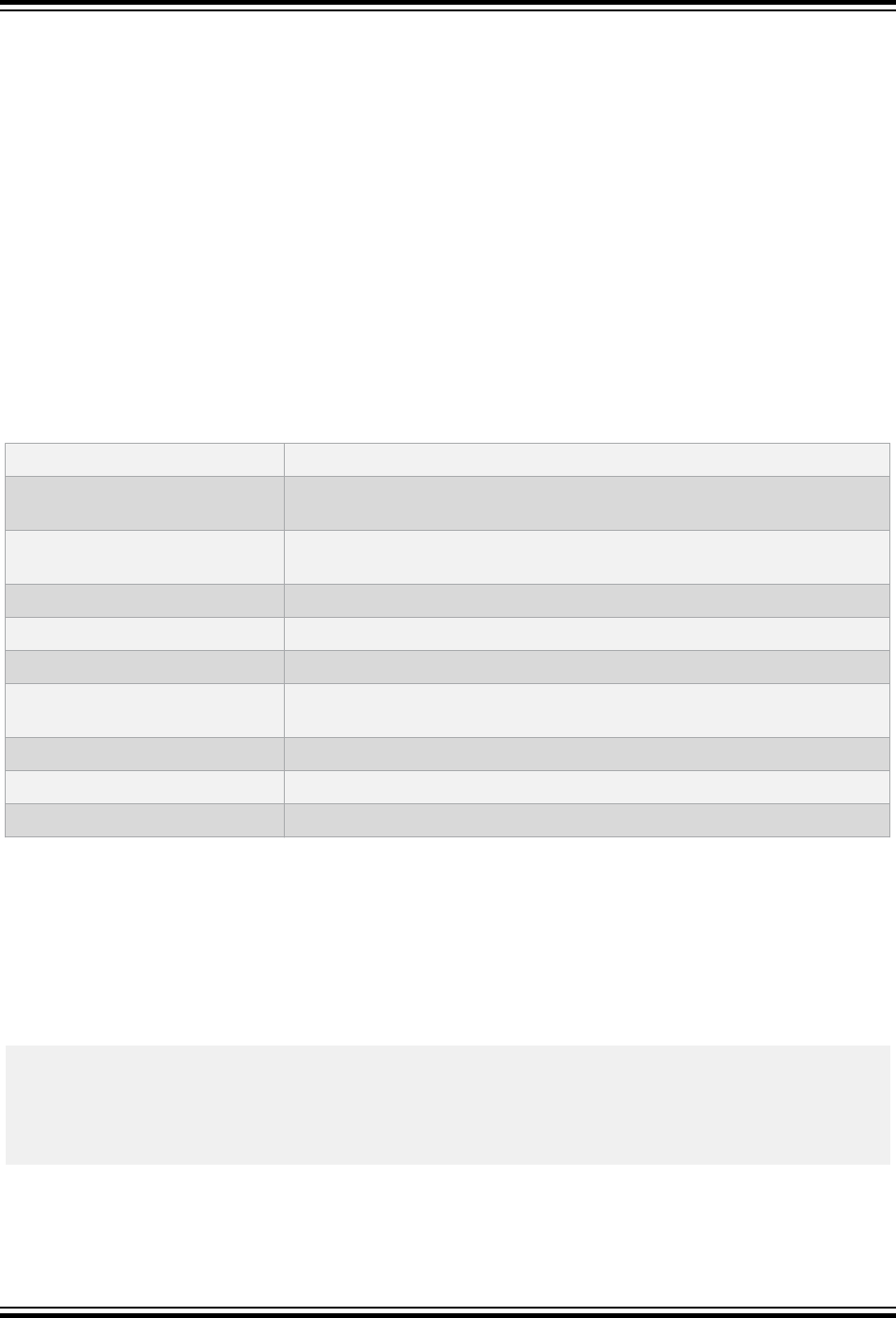

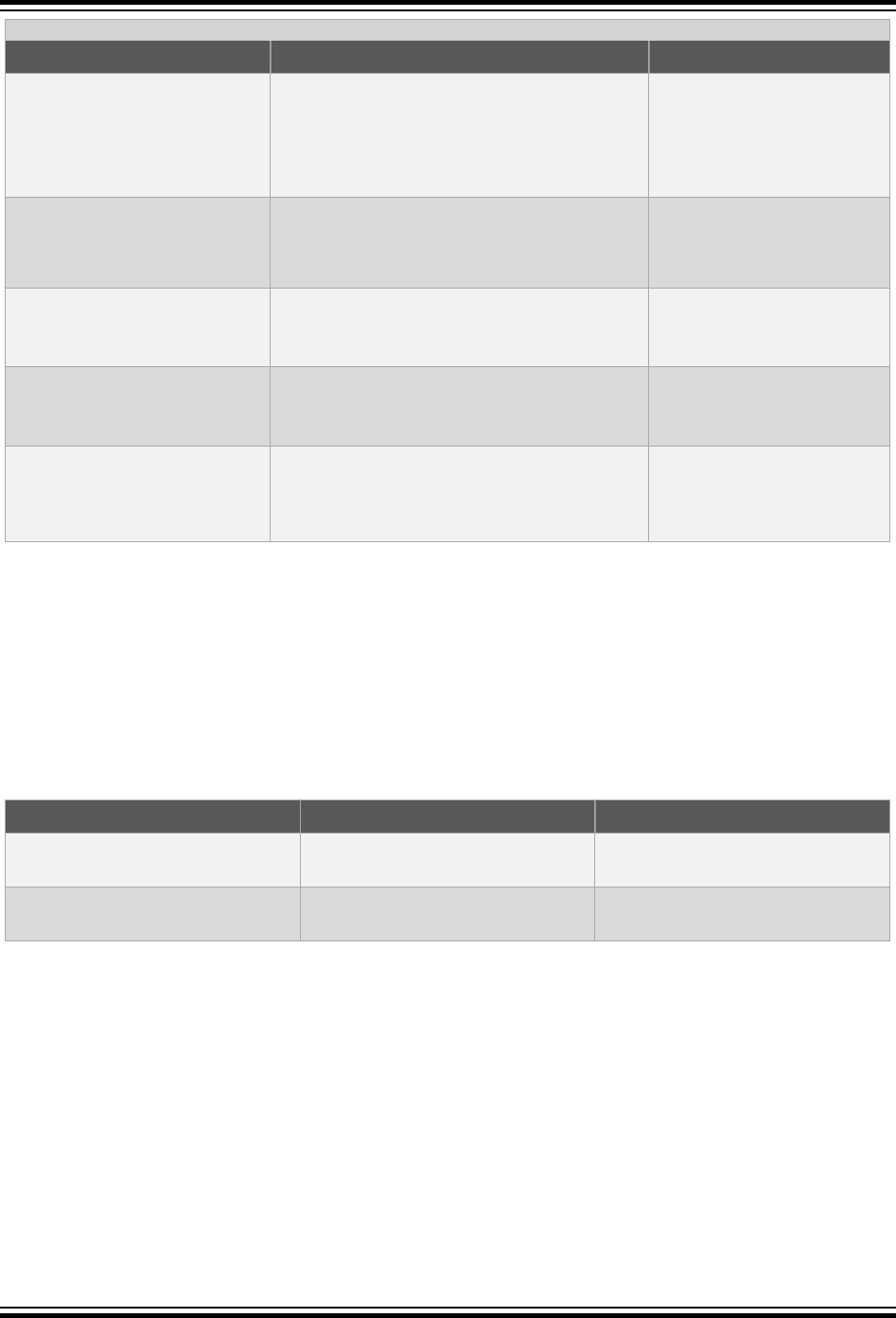

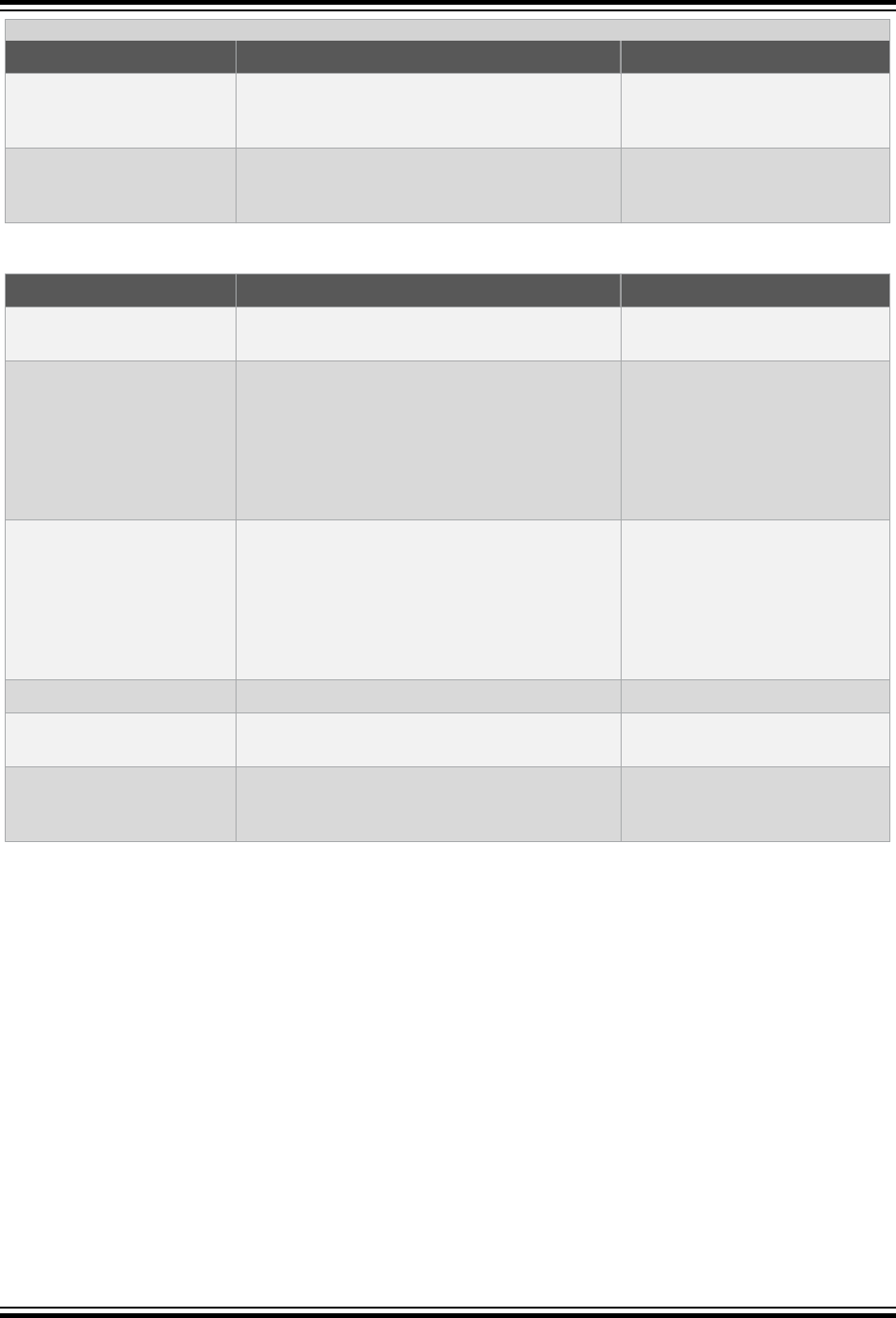

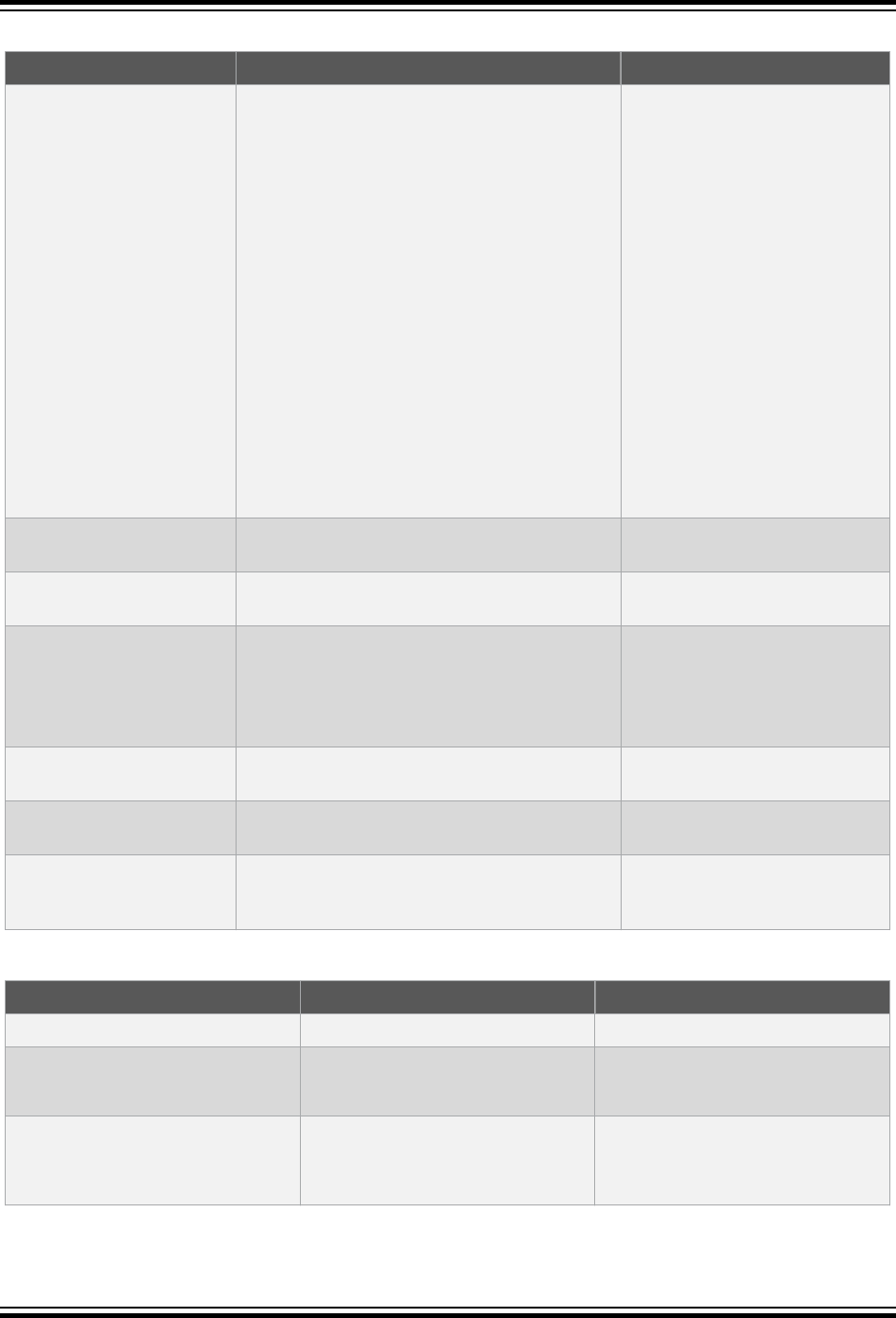

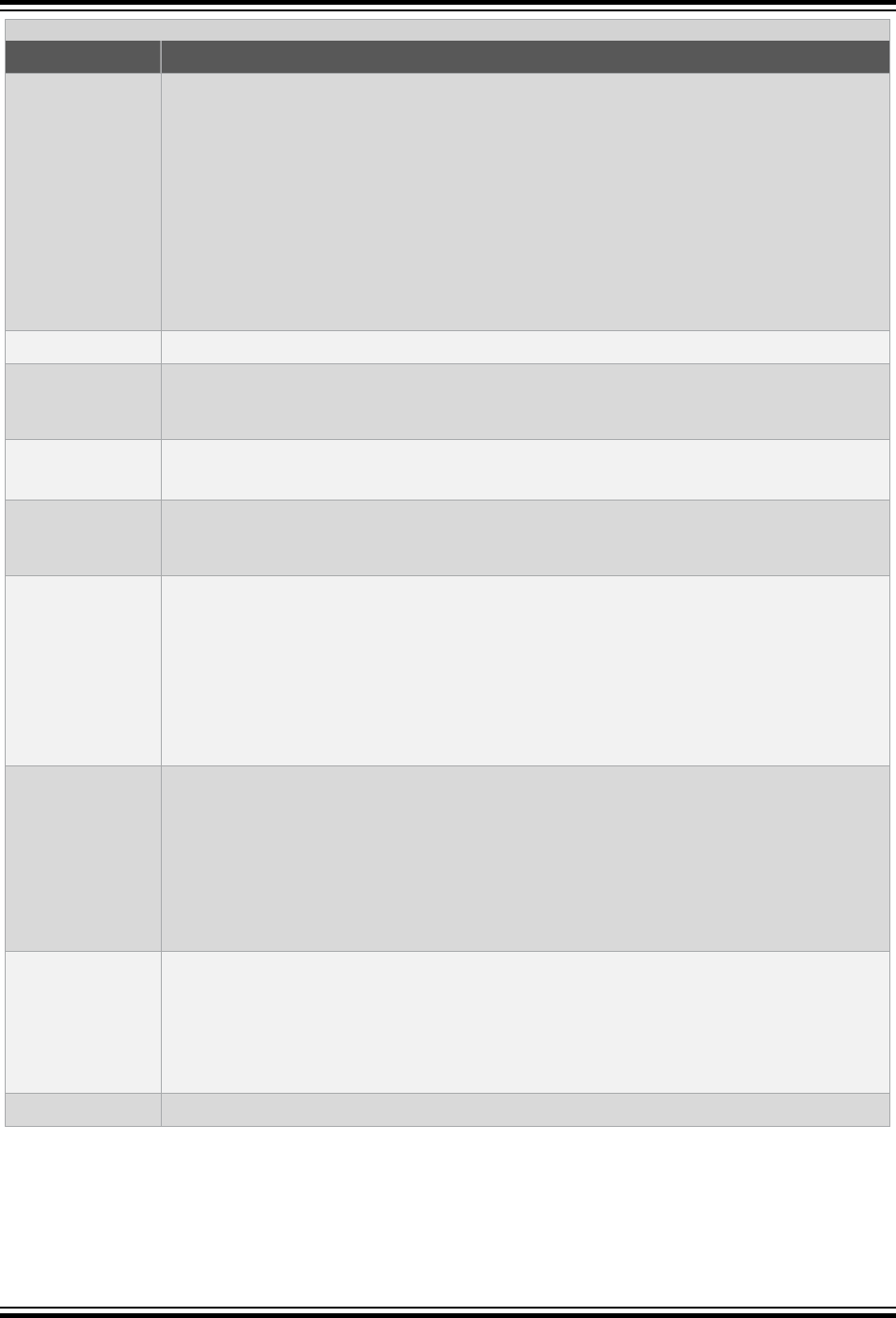

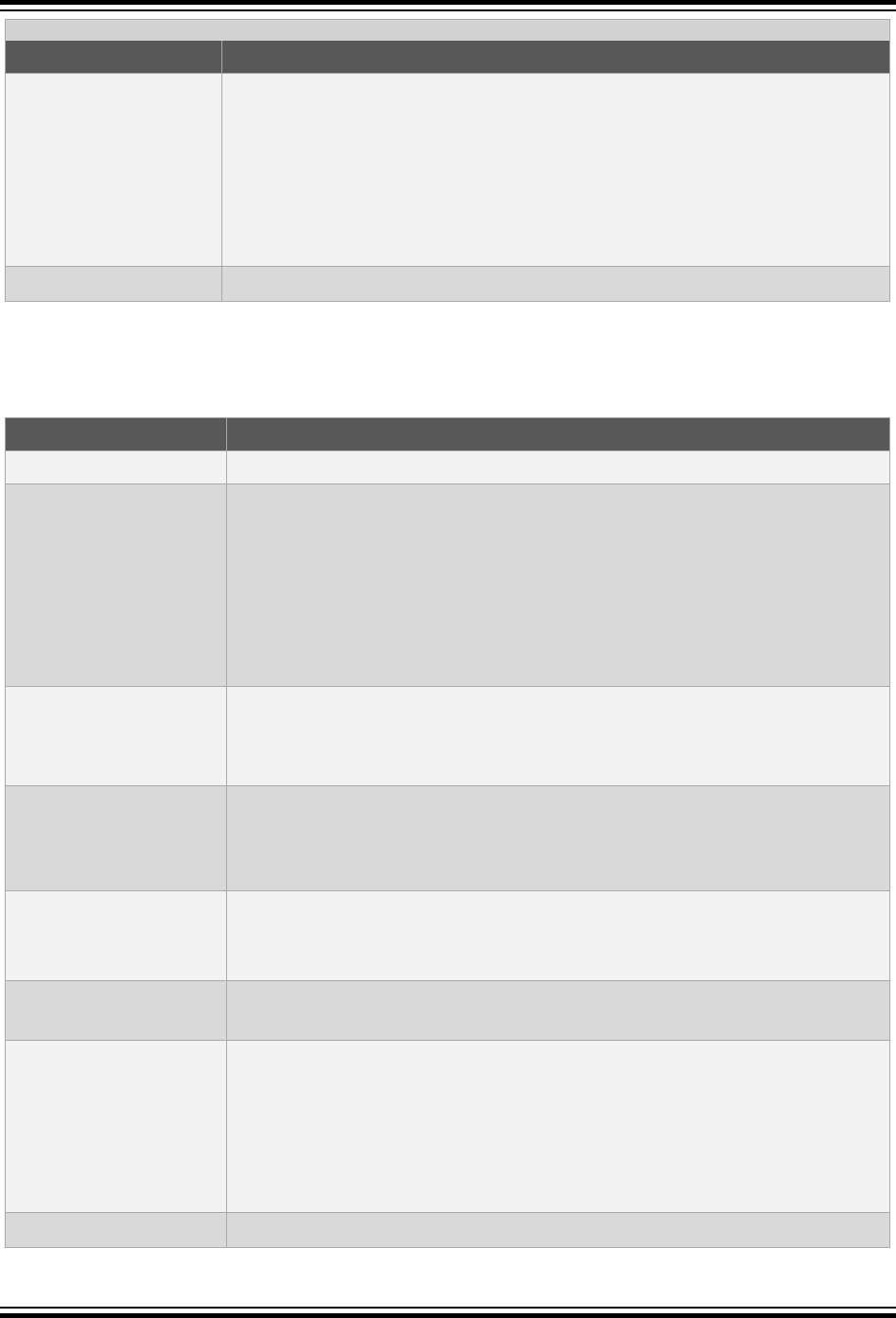

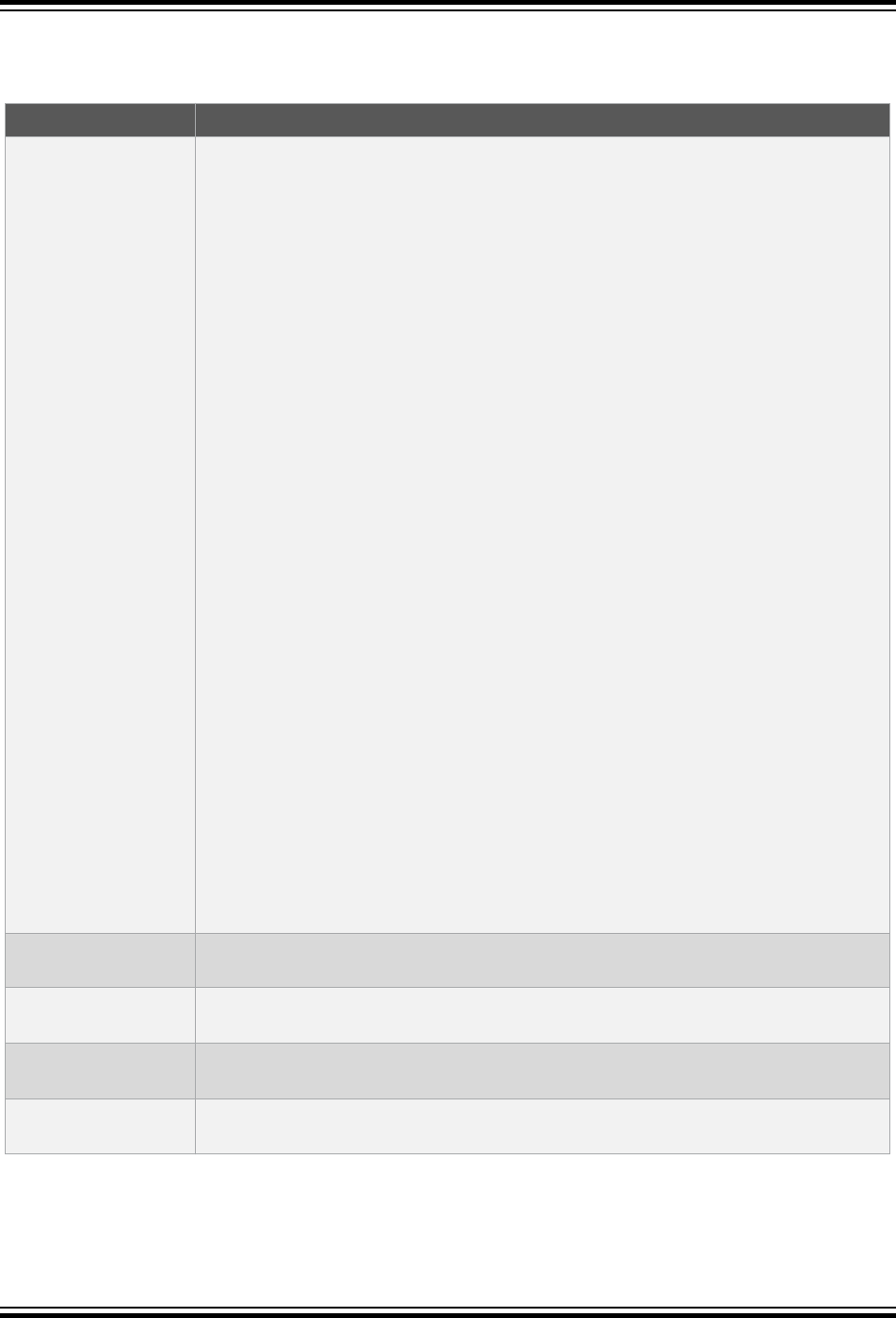

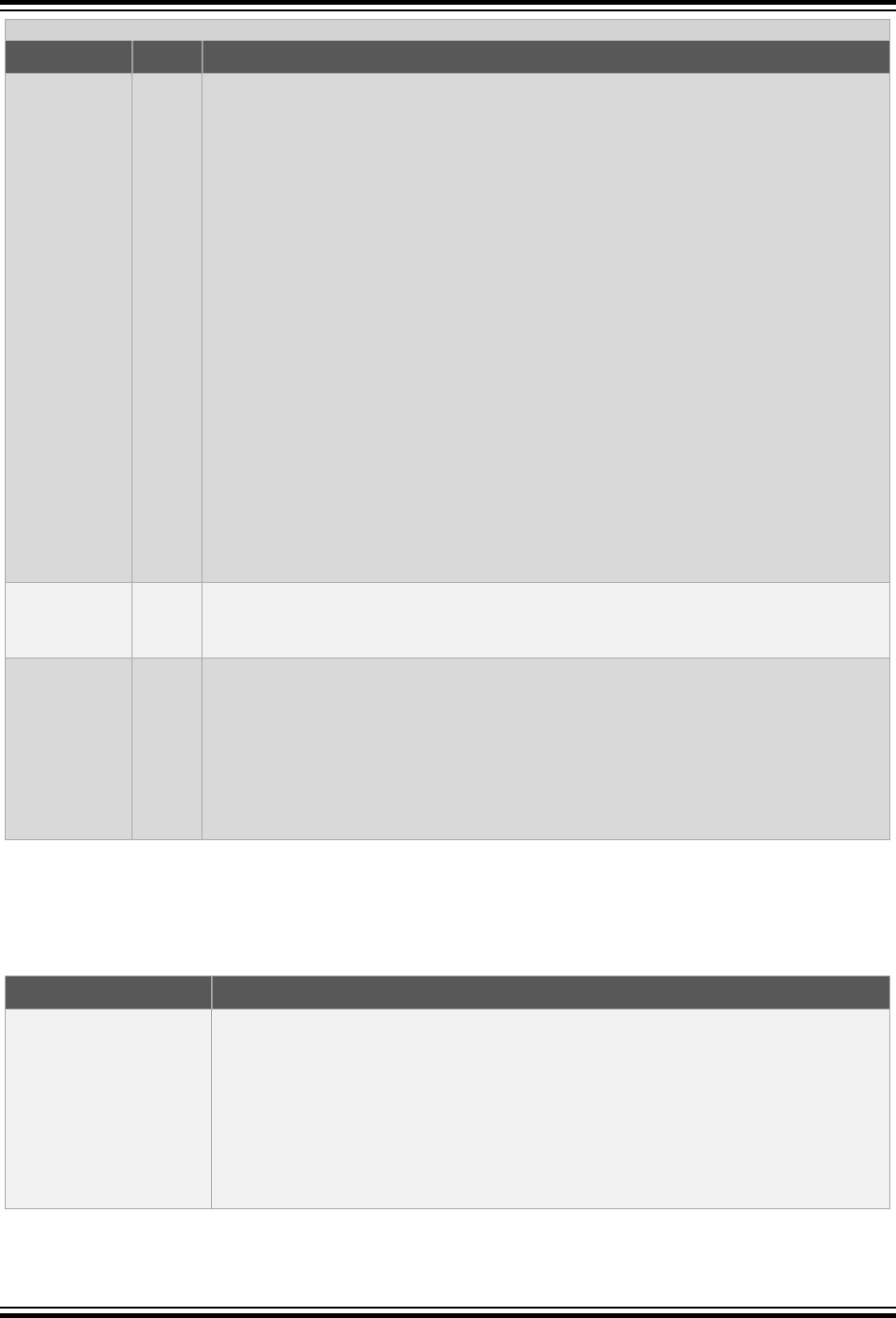

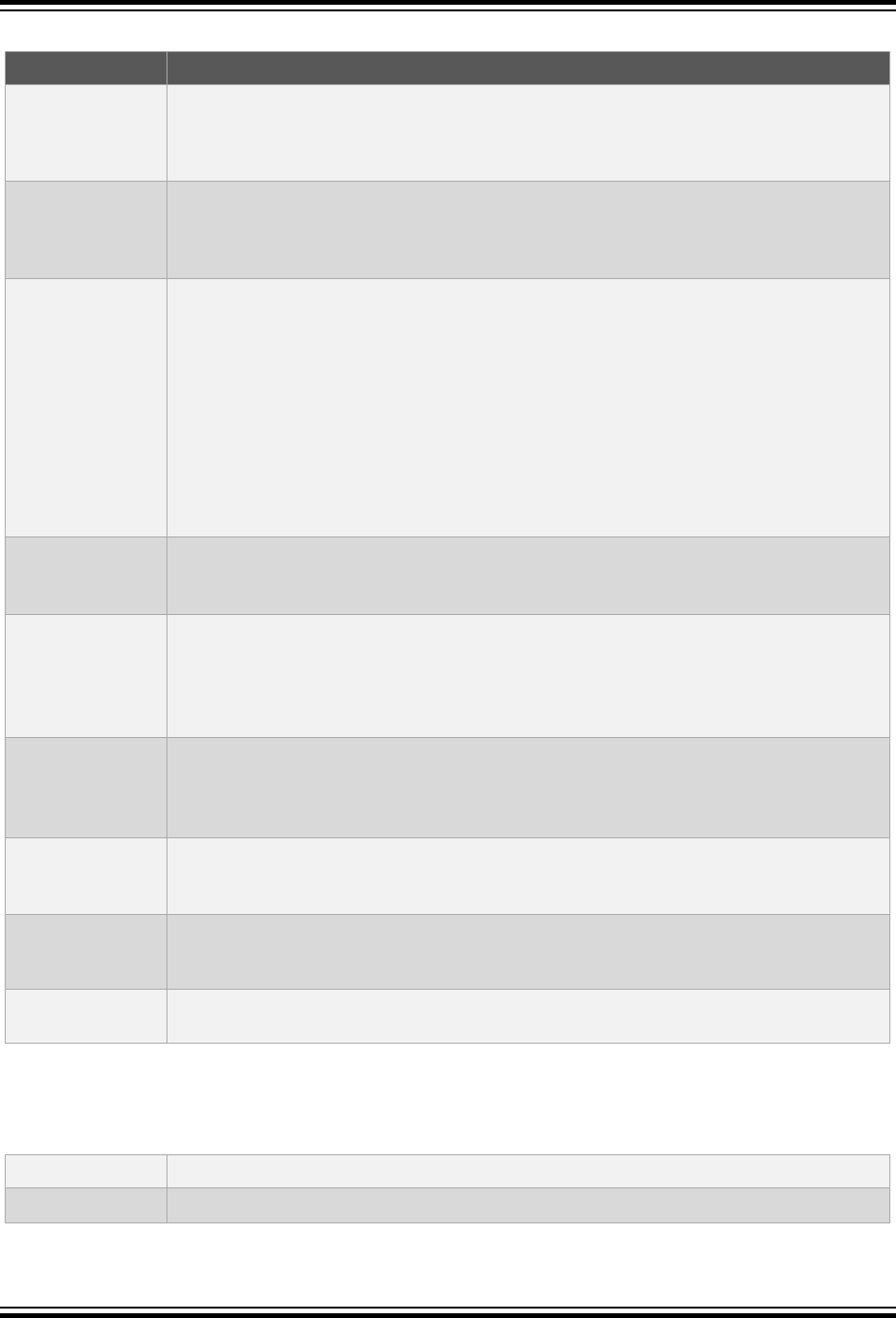

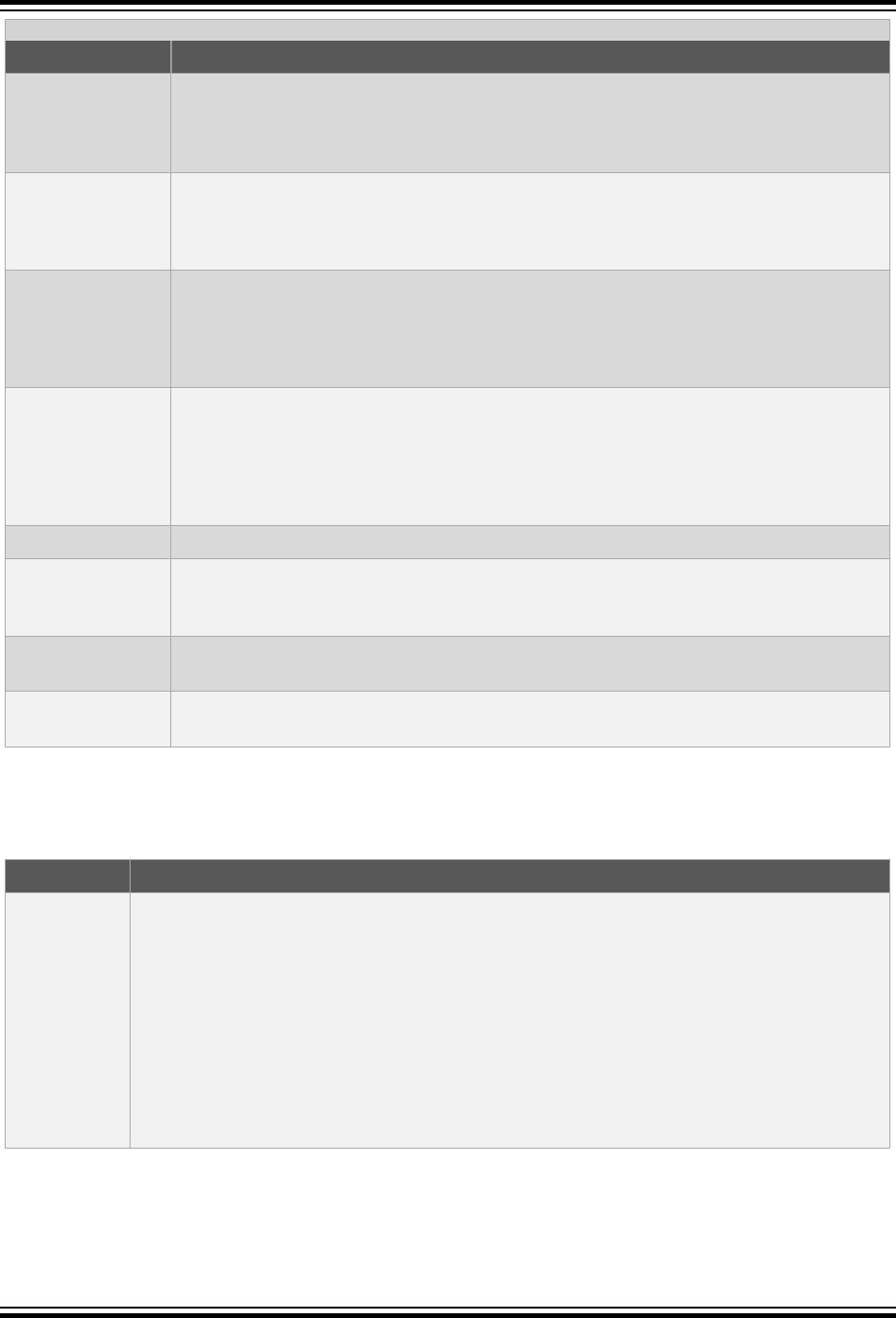

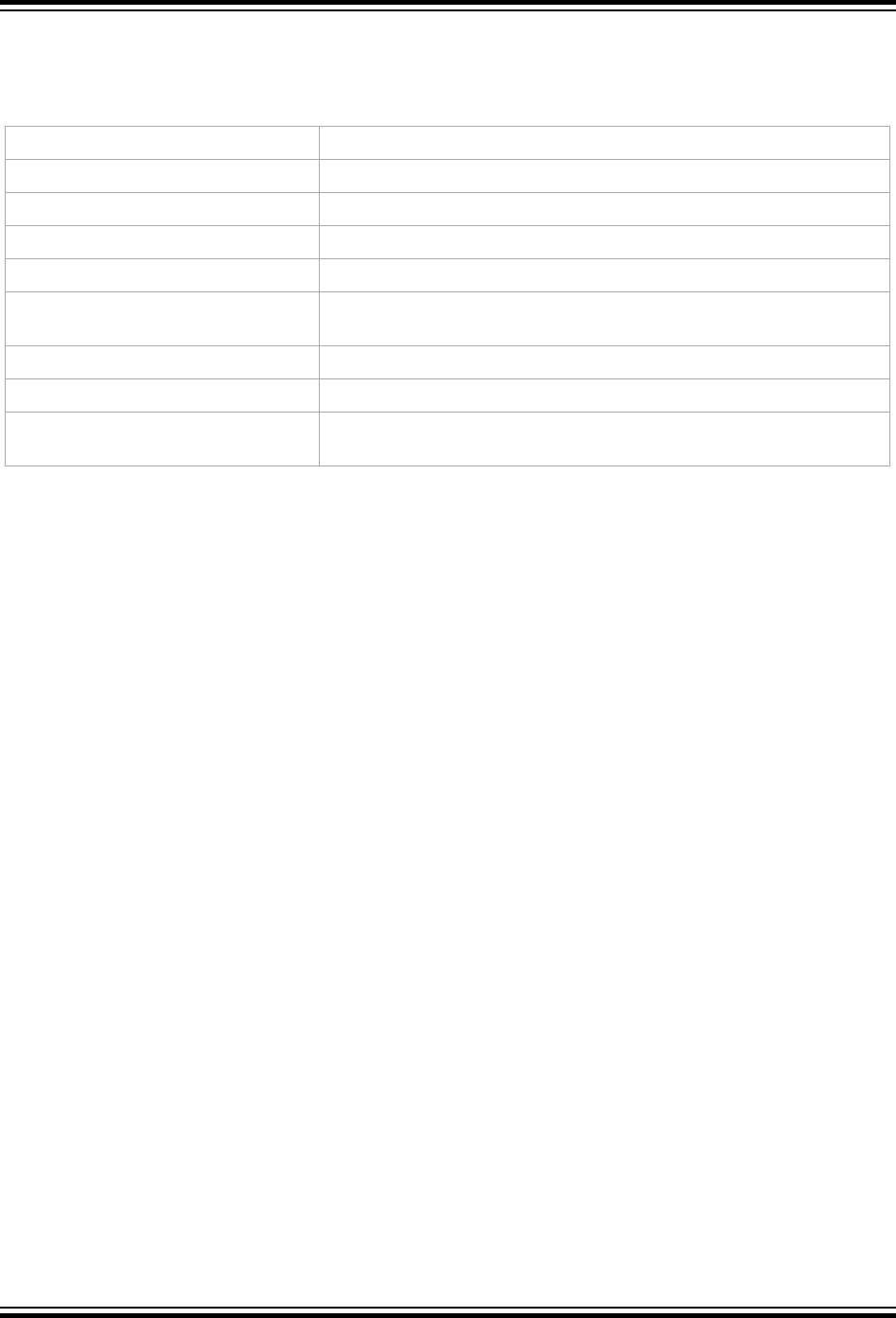

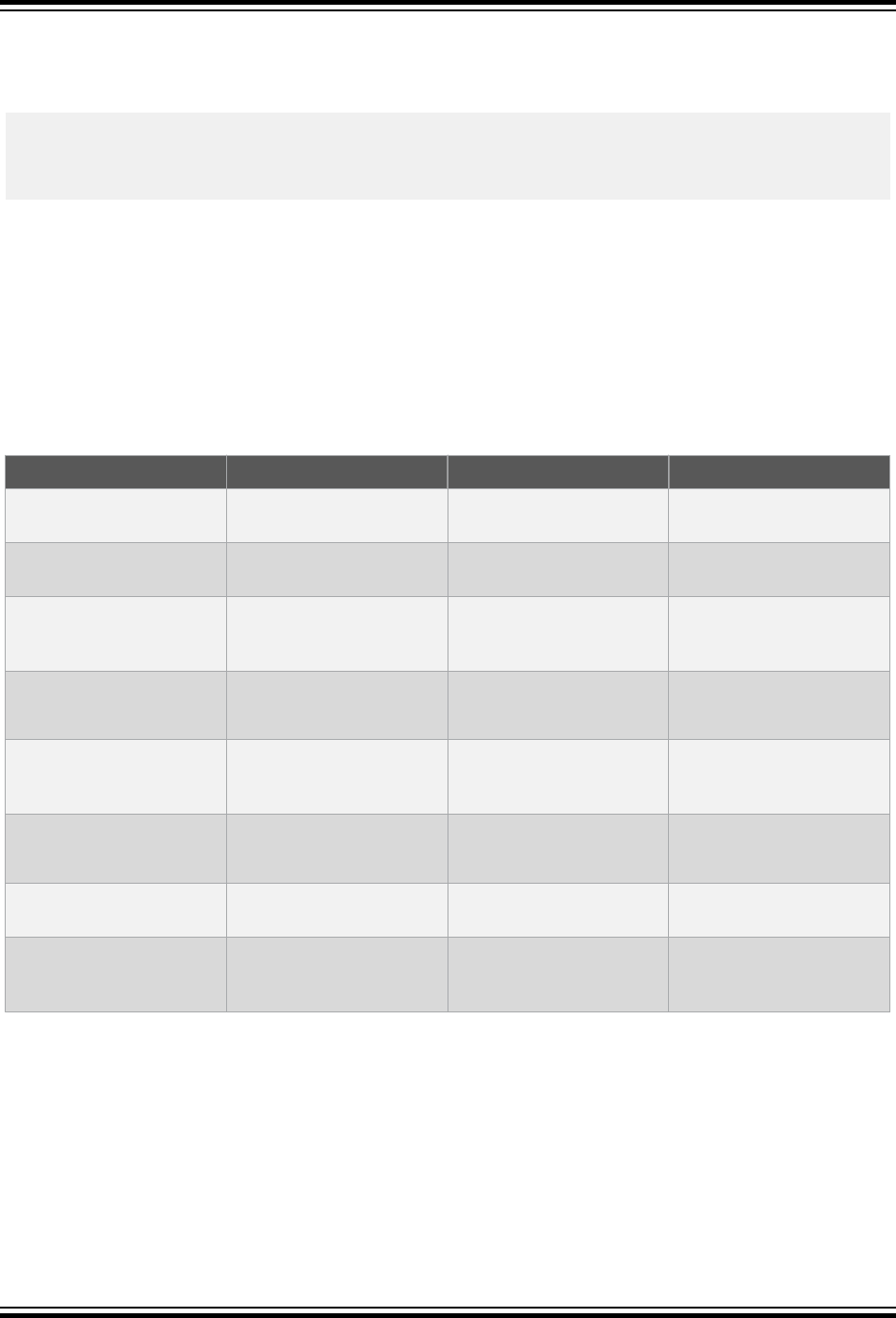

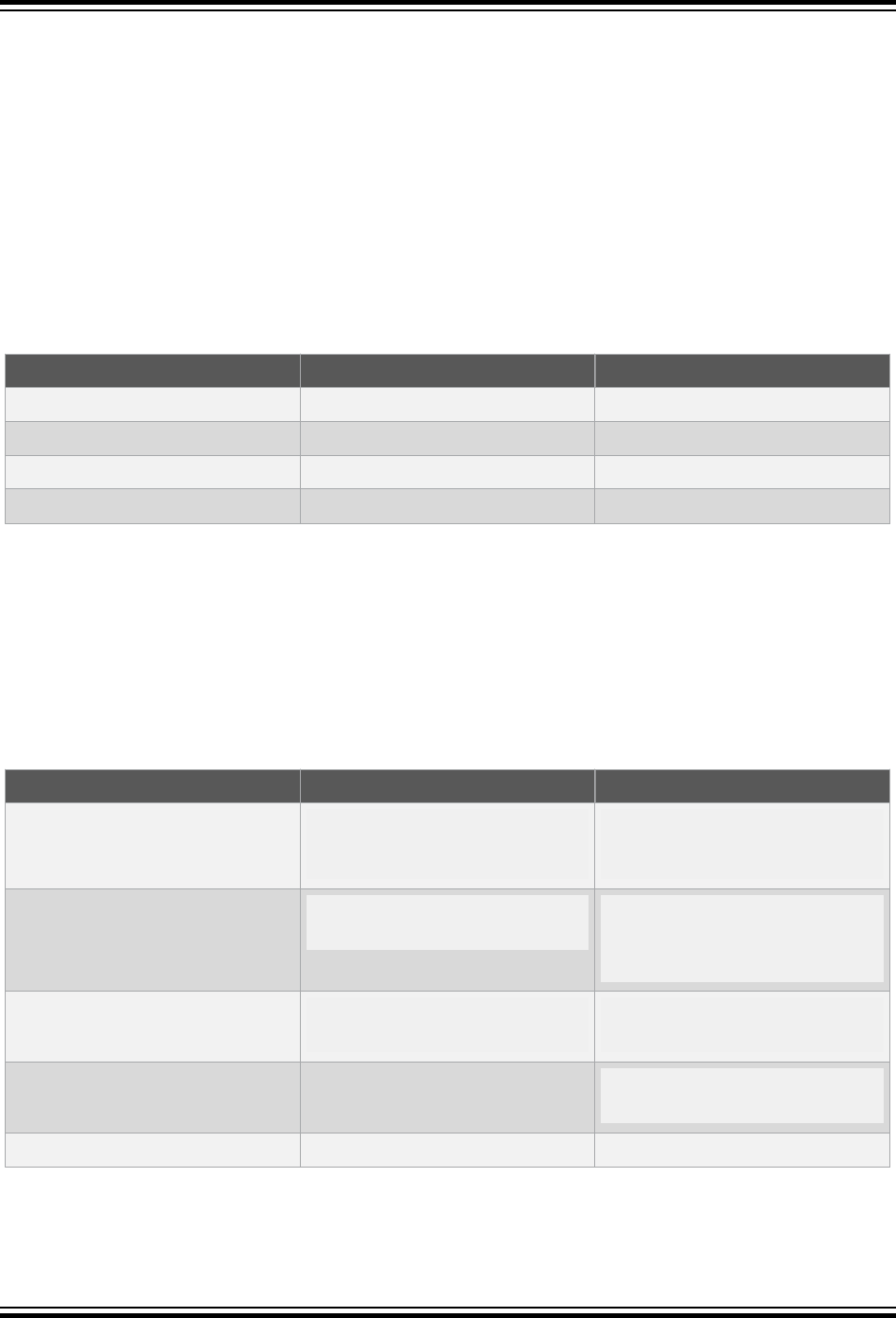

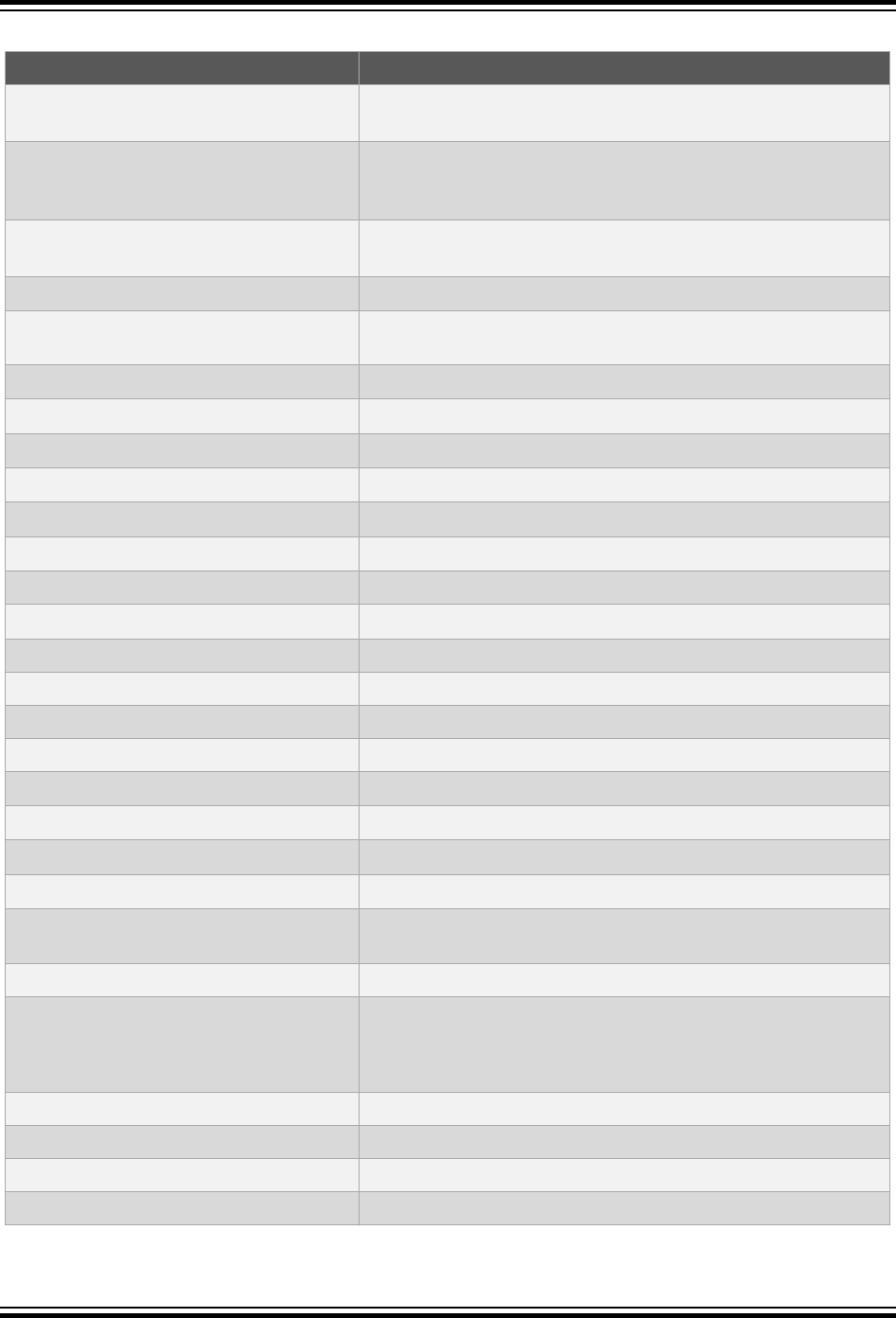

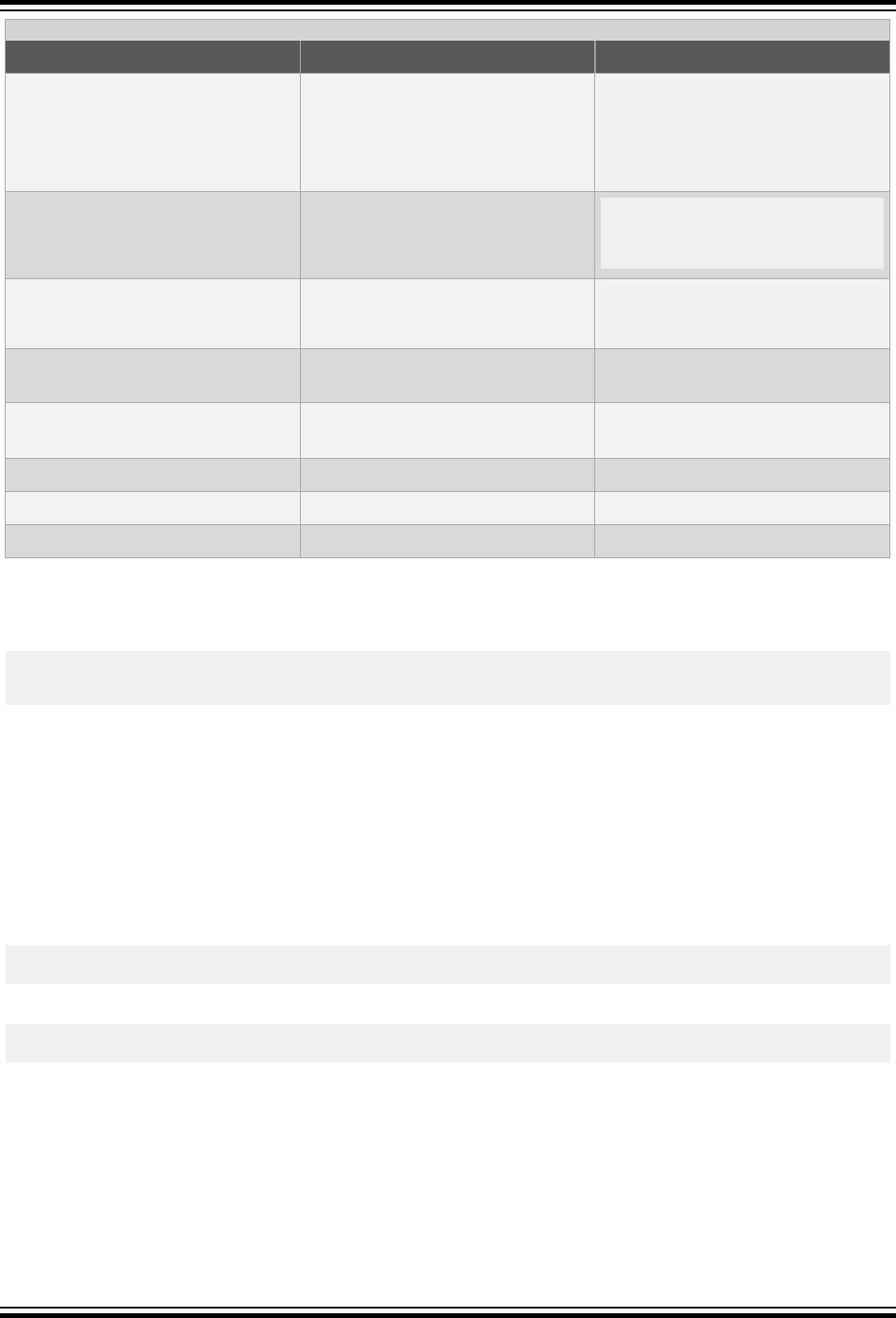

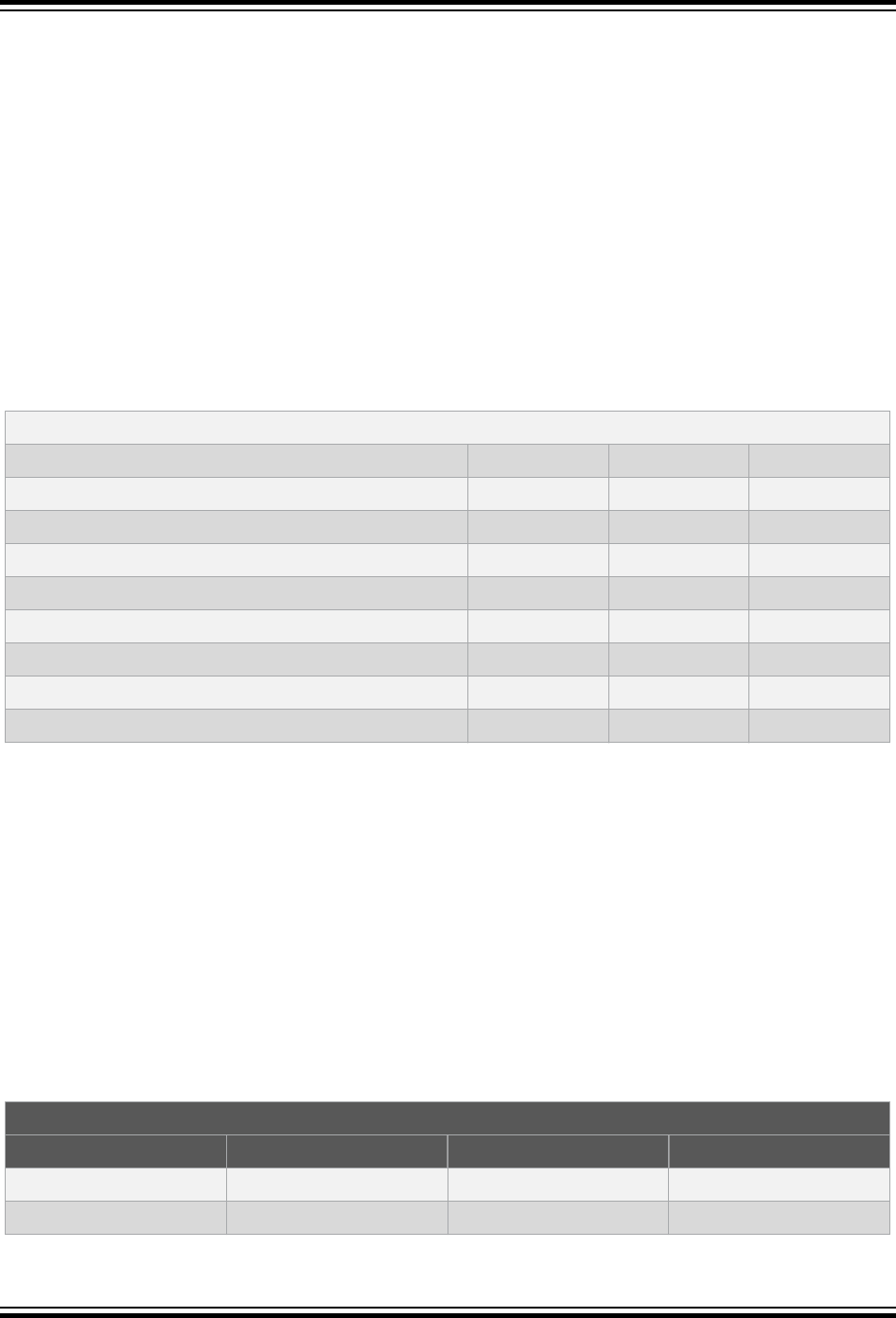

Table 1-1. Documentation Conventions

Description Represents Examples

Arial font:

Italic characters Referenced books MPLAB

®

IDE User’s Guide

Emphasized text ...is the only compiler...

Initial caps A window the Output window

A dialog the Settings dialog

A menu selection select Enable Programmer

Quotes A field name in a window or dialog “Save project before build”

Underlined, italic text with right

angle bracket

A menu path File>Save

Bold characters A dialog button Click OK

A tab Click the Power tab

N‘Rnnnn A number in verilog format, where

N is the total number of digits, R is

the radix and n is a digit.

4‘b0010, 2‘hF1

Text in angle brackets < > A key on the keyboard Press <Enter>, <F1>

Courier New font:

Plain Courier New Sample source code

#define START

Filenames

autoexec.bat

File paths

c:\mcc18\h

Keywords

_asm, _endasm, static

Command-line options

-Opa+, -Opa-

Bit values

0, 1

Constants

0xFF, ‘A’

Italic Courier New A variable argument file.o, where file can be any valid

filename

Square brackets [ ] Optional arguments

mcc18 [options] file [options]

Curly brackets and pipe

character: { | }

Choice of mutually exclusive

arguments; an OR selection

errorlevel {0|1}

XC32 Compiler for PIC32M

Preface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 7

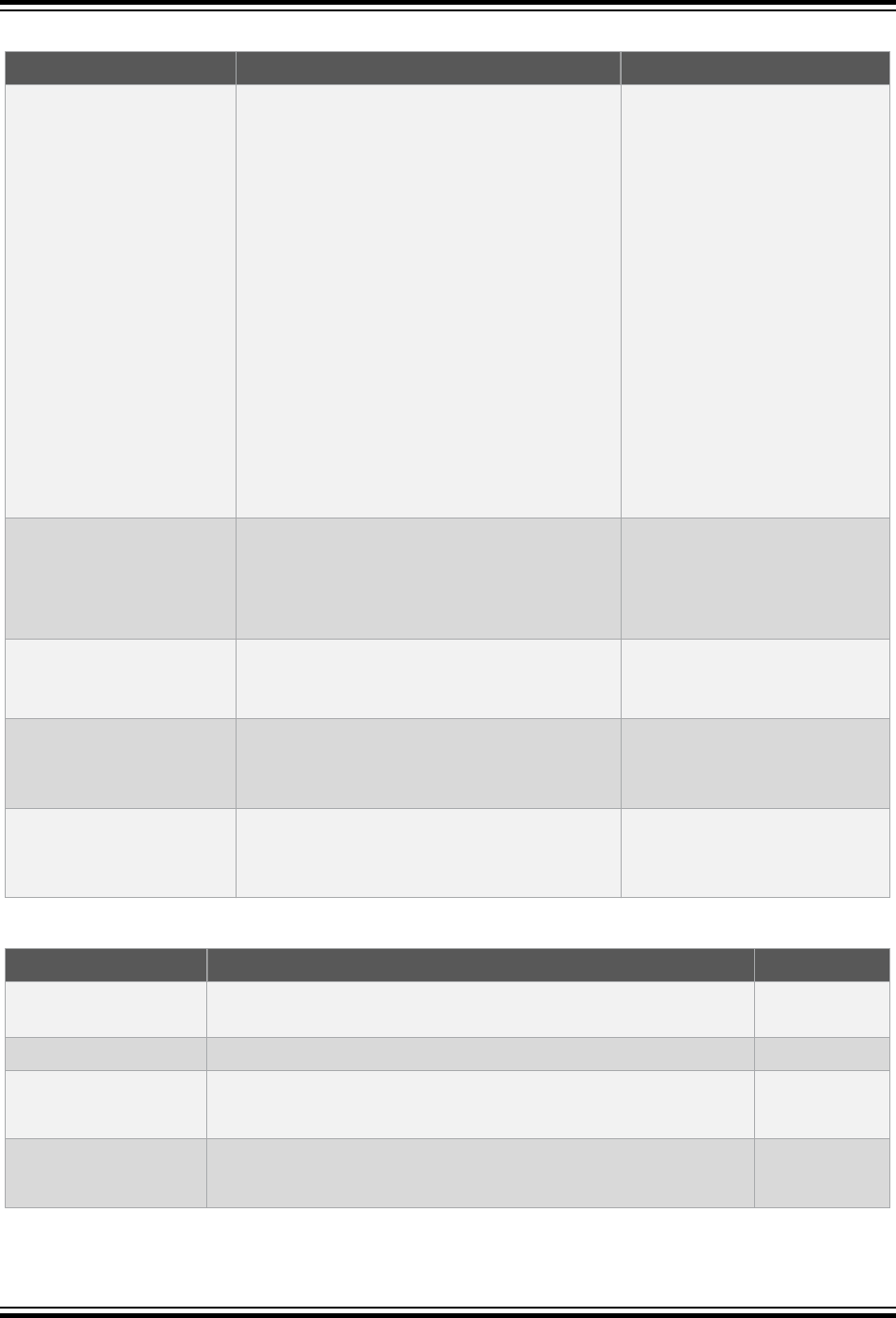

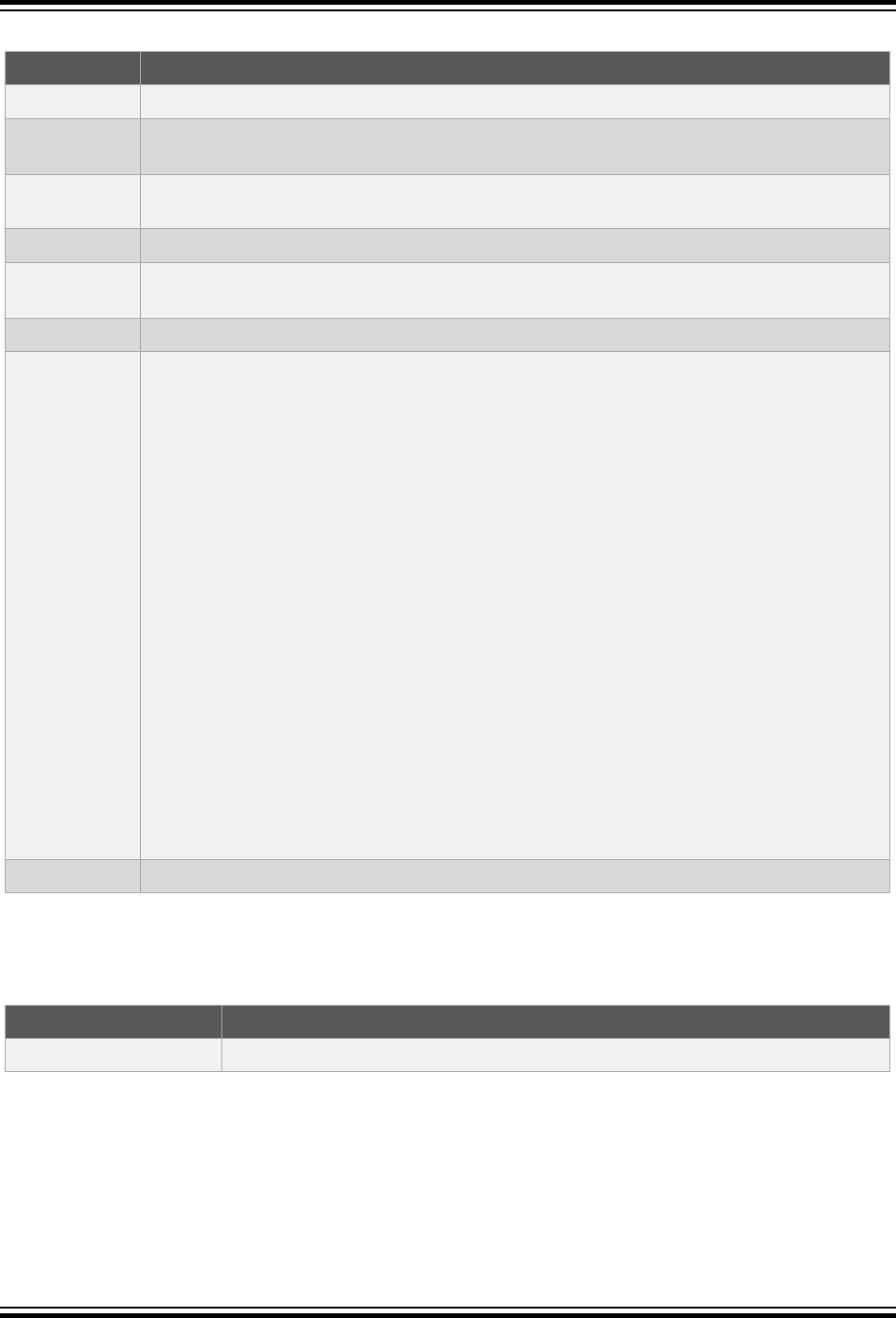

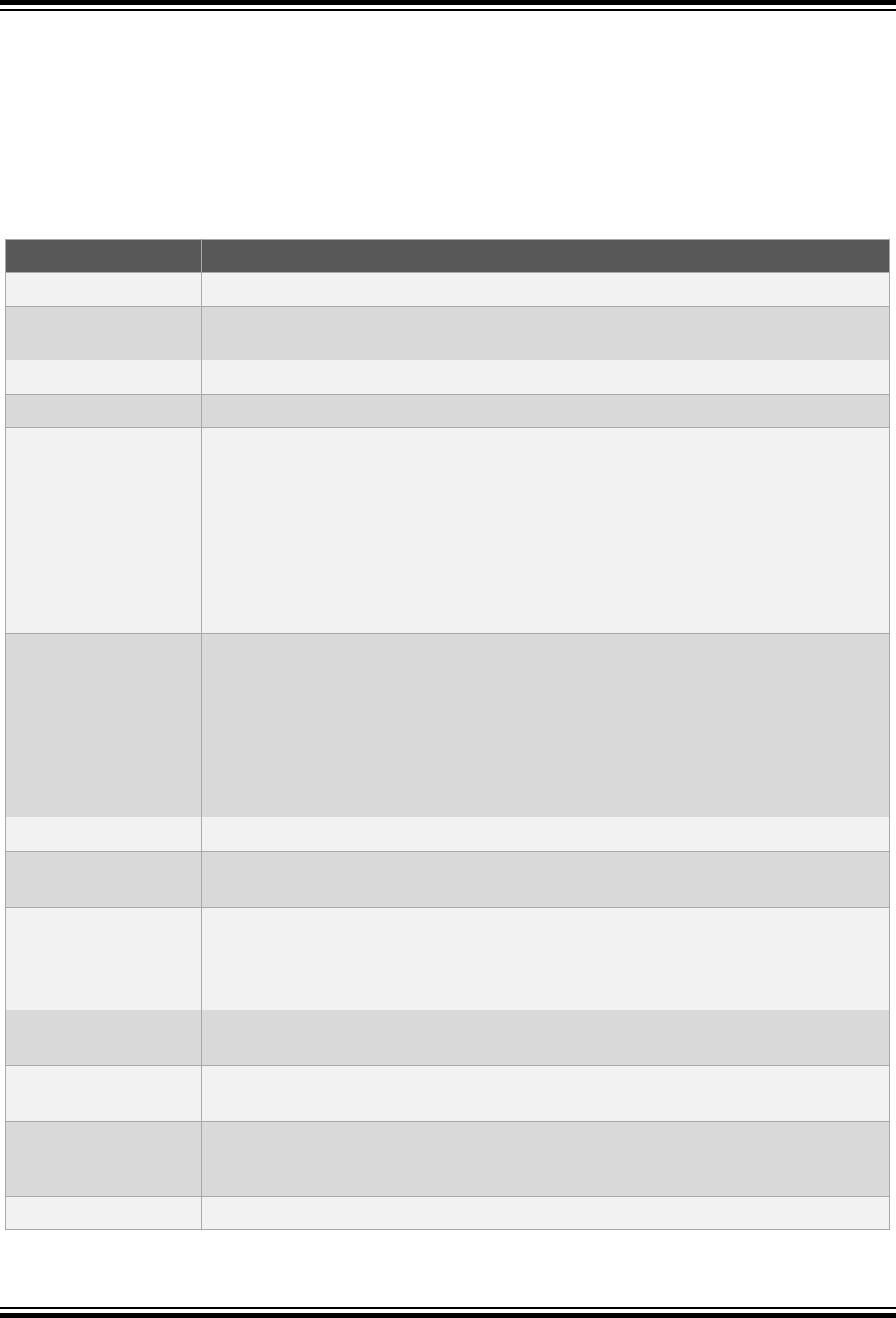

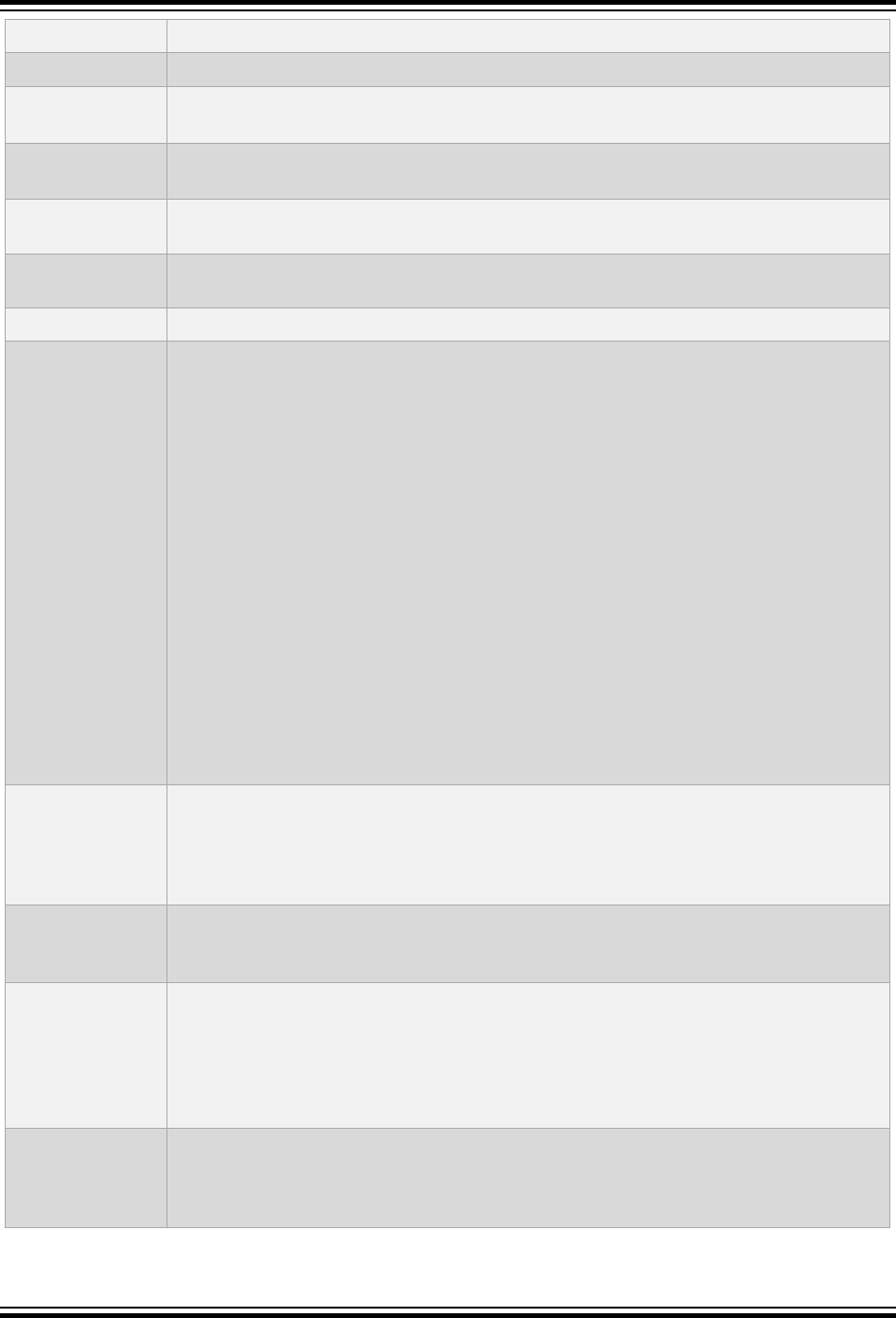

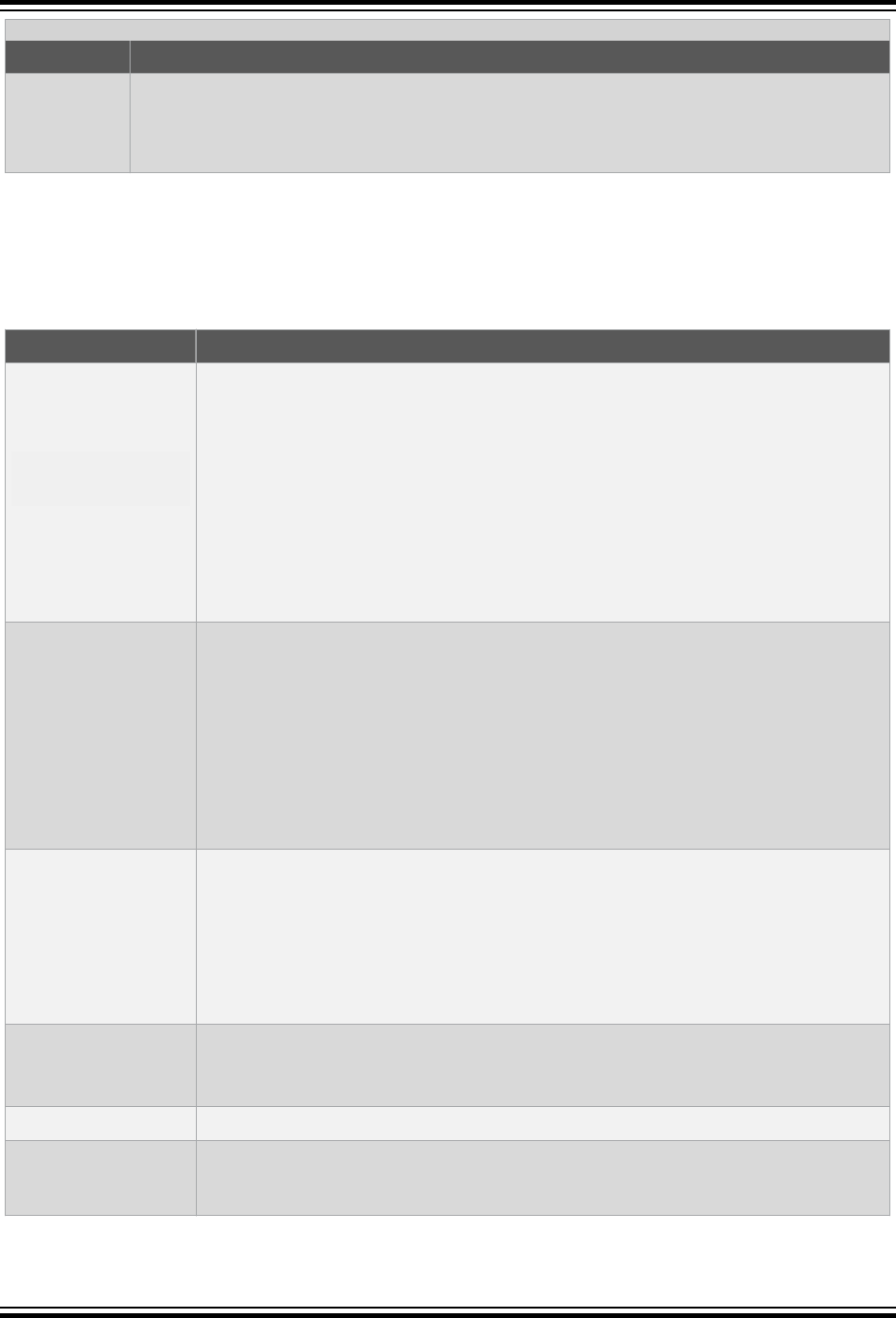

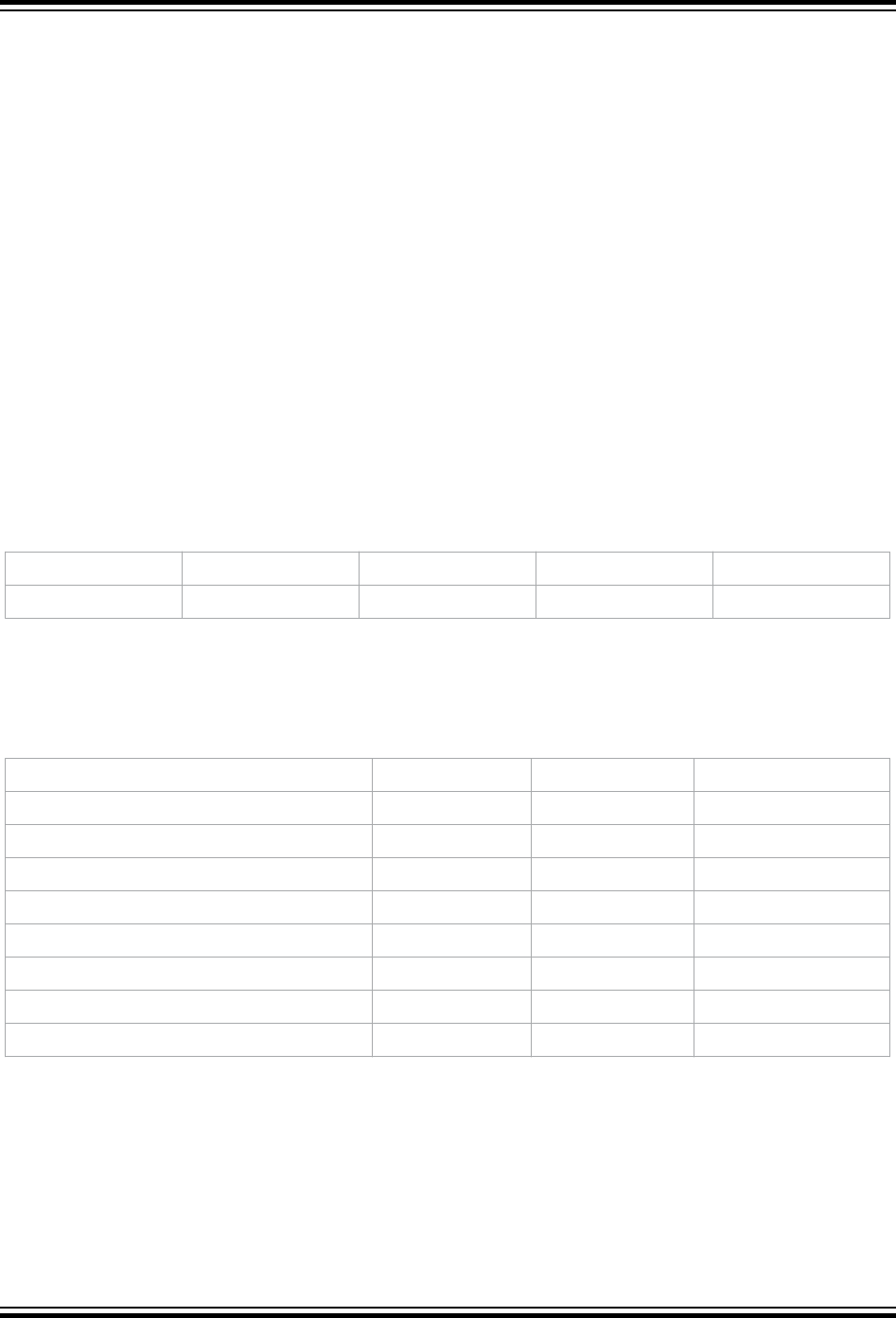

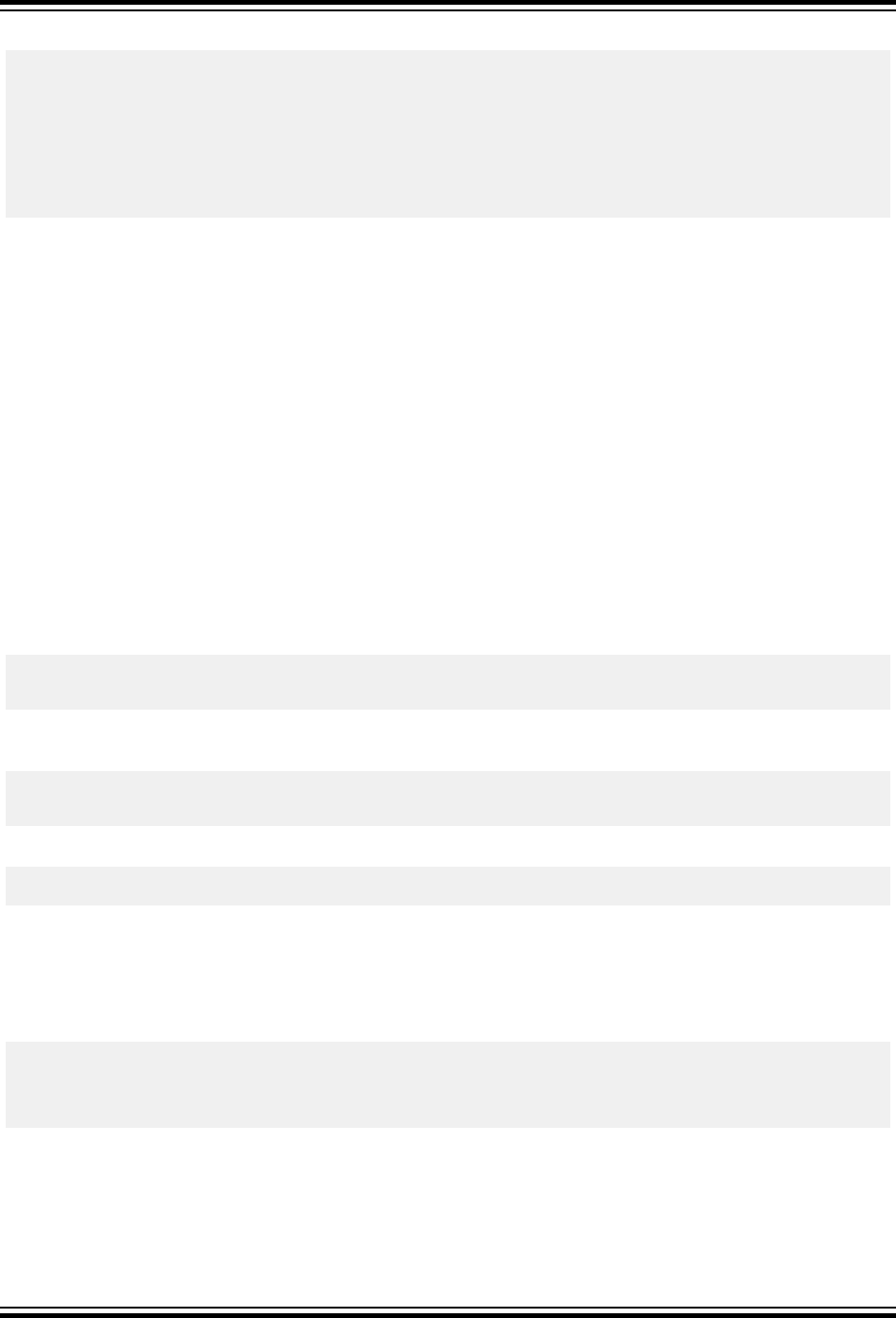

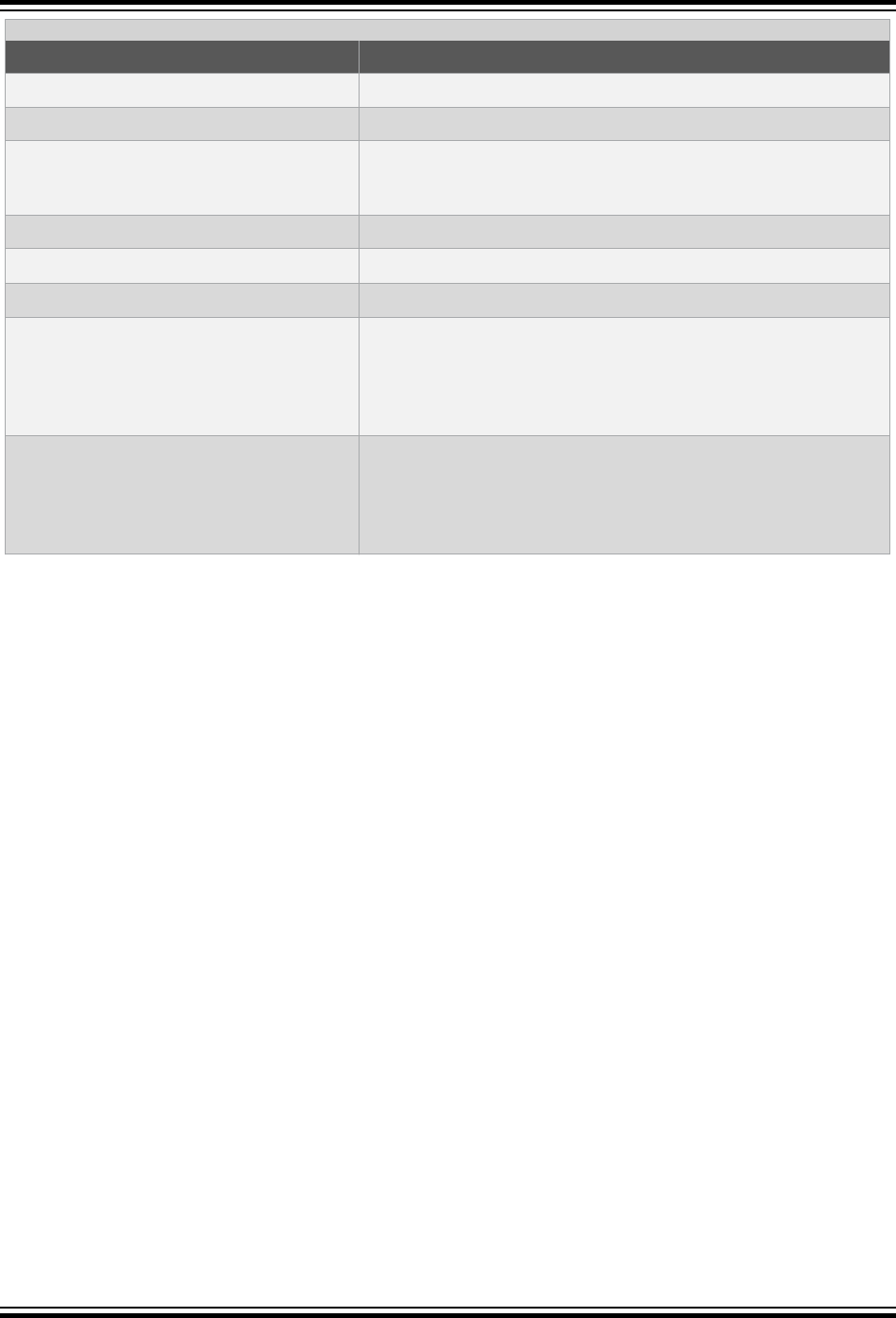

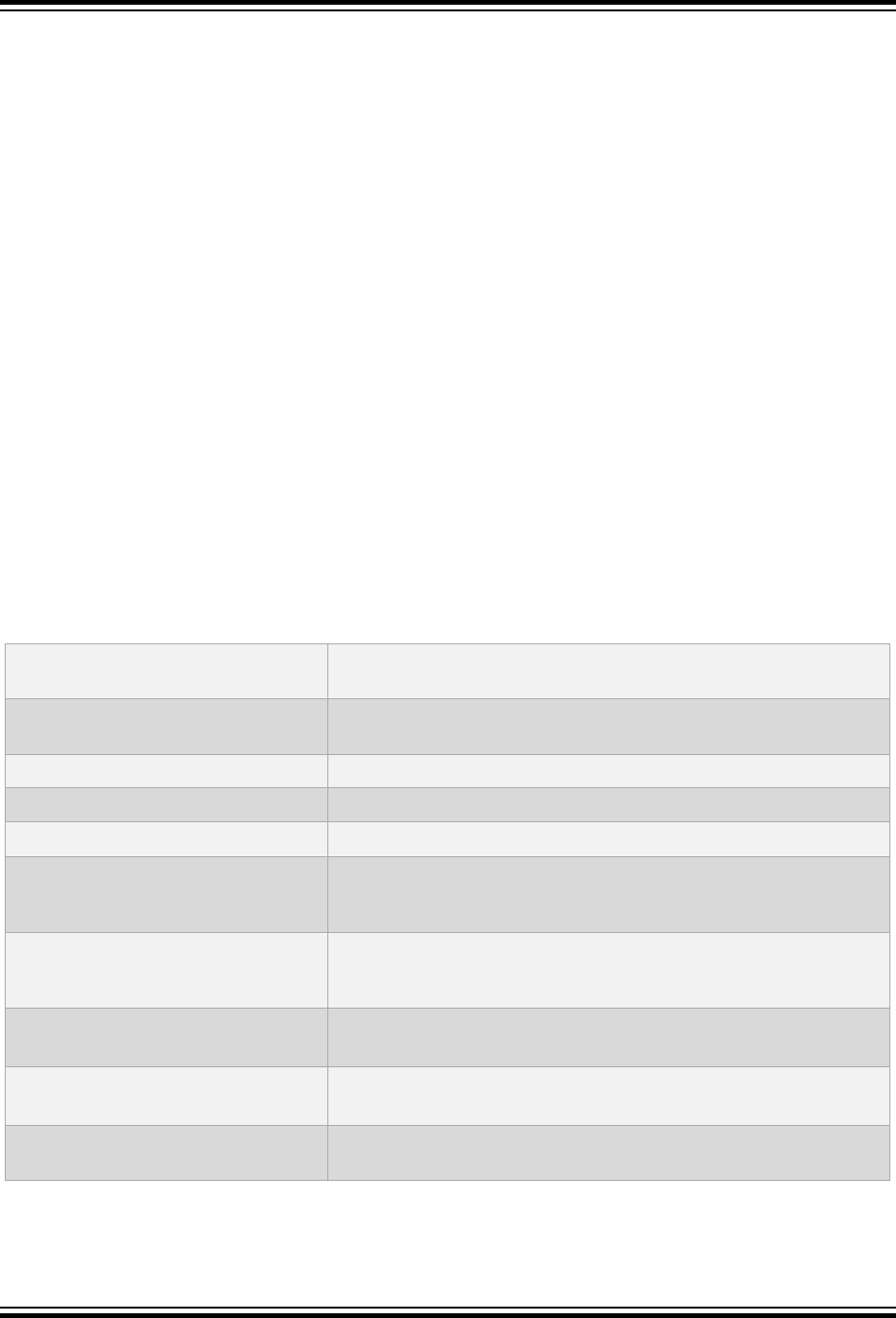

...........continued

Description Represents Examples

Ellipses... Replaces repeated text

var_name [, var_name...]

Represents code supplied by user

void main (void)

{ ...

}

1.2 Recommended Reading

The MPLAB

®

XC32 language toolsuite for PIC32 MCUs consists of a C compilation driver (xc32-gcc), a C++

compilation driver (xc32-g++), an assembler (xc32-as), a linker (xc32-ld), and an archiver/librarian (xc32-ar).

This document describes how to use the MPLAB XC32 C/C++ Compiler. Other useful documents are listed below.

The following Microchip documents are available and recommended as supplemental reference resources.

Release Notes (Readme Files)

For the latest information on Microchip tools, read the associated Release Notes (HTML files) included with the

software.

MPLAB

®

XC32 Assembler, Linker and Utilities User’s Guide (DS50002186)

A guide to using the 32-bit assembler, object linker, object archiver/librarian and various utilities.

32-Bit Language Tools Libraries (DS50001685)

Lists all library functions provided with the MPLAB XC32 C/C++ Compiler with detailed descriptions of their use.

Dinkum Compleat Libraries

The Dinkum Compleat Libraries are organized into a number of headers – files that you include in your program to

declare or define library facilities. A link to the Dinkum libraries is available in the MPLAB X IDE application, on the

My MPLAB X IDE tab, References & Featured Links section.

PIC32 Configuration Settings

Lists the Configuration Bit settings for the Microchip PIC32 devices supported by the #pragma config of the

MPLAB XC32 C/C++ Compiler.

Device-Specific Documentation

The Microchip website contains many documents that describe 32-bit device functions and features. Among these

are:

• Individual and family data sheets

• Family reference manuals

• Programmer’s reference manuals

C Standards Information

American National Standard for Information Systems – Programming Language – C. American National Standards

Institute (ANSI), 11 West 42nd. Street, New York, New York, 10036.

This standard specifies the form and establishes the interpretation of programs expressed in the programming

language C. Its purpose is to promote portability, reliability, maintainability and efficient execution of C language

programs on a variety of computing systems.

C++ Standards Information

Stroustrup, Bjarne, C++ Programming Language: Special Edition, 3rd Edition. Addison-Wesley Professional;

Indianapolis, Indiana, 46240.

ISO/IEC 14882 C++ Standard. The ISO C++ Standard is standardized by ISO (The International Standards

Organization) in collaboration with ANSI (The American National Standards Institute), BSI (The British Standards

Institute) and DIN (The German national standards organization).

XC32 Compiler for PIC32M

Preface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 8

This standard specifies the form and establishes the interpretation of programs expressed in the programming

language C++. Its purpose is to promote portability, reliability, maintainability and efficient execution of C++ language

programs on a variety of computing systems.

C Reference Manuals

Harbison, Samuel P. and Steele, Guy L., C A Reference Manual, Fourth Edition, Prentice-Hall, Englewood Cliffs, N.J.

07632.

Kernighan, Brian W. and Ritchie, Dennis M., The C Programming Language, Second Edition. Prentice Hall,

Englewood Cliffs, N.J. 07632.

Kochan, Steven G., Programming In ANSI C, Revised Edition. Hayden Books, Indianapolis, Indiana 46268.

Plauger, P.J., The Standard C Library, Prentice-Hall, Englewood Cliffs, N.J. 07632.

Van Sickle, Ted., Programming Microcontrollers in C, First Edition. LLH Technology Publishing, Eagle Rock, Virginia

24085.

GCC Documents

http://gcc.gnu.org/onlinedocs/

http://sourceware.org/binutils/

XC32 Compiler for PIC32M

Preface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 9

2. Compiler Overview

The MPLAB

®

XC32 C/C++ Compiler for PIC32M MCUs is defined and described in this section.

2.1 Device Description

The MPLAB XC32 C/C++ Compiler fully supports most Microchip PIC32M and MEC 14 devices.

2.2 Compiler Description and Documentation

The MPLAB XC32 C/C++ Compiler is a full-featured, optimizing compiler that translates standard ANSI C programs

into 32-bit device assembly language source. The toolchain supports both the PIC32M microcontroller family. The

compiler also supports many command-line options and language extensions that allow full access to the 32-bit

device hardware capabilities, and affords fine control of the compiler code generator.

The compiler is a port of the GCC compiler from the Free Software Foundation.

The compiler is available for several popular operating systems, including 32- and 64-bit Windows

®

, Linux

®

and Mac

OS

®

X.

The compiler can run in Free or PRO operating mode. The PRO operating mode is a licensed mode and requires an

activation key and Internet connectivity to enable it. Free mode is available for unlicensed customers. The basic

compiler operation, supported devices and available memory are identical across all modes. The modes only differ in

the level of optimization employed by the compiler.

2.2.1 Conventions

Throughout this manual, the term “the compiler” is often used. It can refer to either all or some subset of the collection

of applications that form the MPLAB XC32 C/C++ Compiler. Often it is not important to know, for example, whether

an action is performed by the parser or code generator application and it is sufficient to say it was performed by “the

compiler.”

It is also reasonable for “the compiler” to refer to the command-line driver (or just driver) as this is the application that

is always executed to invoke the compilation process. The driver for the MPLAB XC32 C/C++ Compiler package is

called xc32-gcc. The driver for the C/ASM projects is also xc32-gcc. The driver for C/C++/ASM projects is xc32-

g++. The drivers and their options are discussed in 6.7 Driver Option Descriptions. Following this view, “compiler

options” should be considered command-line driver options, unless otherwise specified in this manual.

Similarly “compilation” refers to all, or some part of, the steps involved in generating source code into an executable

binary image.

2.2.2 ANSI C Standards

The compiler is a fully validated compiler that conforms to the ANSI C standard as defined by the ANSI specification

(ANSI x3.159-1989) and described in Kernighan and Ritchie’s The C Programming Language (second edition). The

ANSI standard includes extensions to the original C definition that are now standard features of the language. These

extensions enhance portability and offer increased capability. In addition, language extensions for PIC32 MCU

embedded-control applications are included.

2.2.3 Optimization

The compiler uses a set of sophisticated optimization passes that employ many advanced techniques for generating

efficient, compact code from C/C++ source. The optimization passes include high-level optimizations that are

applicable to any C/C++ code, as well as PIC32 MCU-specific optimizations that take advantage of the particular

features of the device architecture.

For more on optimizations, see 19. Optimizations.

2.2.4 ANSI Standard Library Support

The compiler is distributed with a complete ANSI C standard library. All library functions have been validated and

conform to the ANSI C library standard. The library includes functions for string manipulation, dynamic memory

XC32 Compiler for PIC32M

Compiler Overview

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 10

allocation, data conversion, timekeeping and math functions (trigonometric, exponential and hyperbolic). The

standard I/O functions for file handling are also included, and, as distributed, they support full access to the host file

system using the command-line simulator. The fully functional source code for the low-level file I/O functions is

provided in the compiler distribution, and may be used as a starting point for applications that require this capability.

2.2.5 ISO/IEC C++ Standard

The compiler is distributed with the 2003 Standard C++ Library.

Note: Do not specify an MPLAB XC32 system include directory (for example, /pic32mx/include/) in your

project properties.The xc32-gcc compilation drivers automatically select the XC libc and their respective include-file

directory for you. The xc32-g++ compilation drivers automatically select the Dinkumware libc and their respective

include-file directory for you. The Dinkum C libraries can only be used with the C++ compiler. Manually adding a

system include file path may disrupt this mechanism and cause the incorrect libc include files to be compiled into your

project, causing a conflict between the include files and the library. Note that adding a system include path to your

project properties has never been a recommended practice.

2.2.6 Compiler Driver

The compiler includes a powerful command-line driver program. Using the driver program, application programs can

be compiled, assembled and linked in a single step.

2.2.7 Documentation

This version of the C compiler is supported under MPLAB X IDE v5.05 or higher is required.

2.3 Compiler and Other Development Tools

The compiler works with many other Microchip tools including:

• MPLAB XC32 assembler and linker - see the “MPLAB

®

XC32 Assembler, Linker and Utilities User’s Guide”

(DS50002186).

• MPLAB X IDE (v5.05 or higher).

• The MPLAB Simulator.

• All Microchip debug tools and programmers.

• Demo boards and starter kits that support 32-bit devices.

XC32 Compiler for PIC32M

Compiler Overview

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 11

3. Common C Interface

The Common C Interface (CCI) is available with all MPLAB XC C compilers and is designed to enhance code

portability between these compilers. For example, CCI-conforming code would make it easier to port from a PIC18

MCU using the MPLAB XC8 C compiler to a PIC32 MCU using the MPLAB XC32 C/C++ Compiler.

The CCI assumes that your source code already conforms to the ANSI Standard. If you intend to use the CCI, it is

your responsibility to write code that conforms. Legacy projects will need to be migrated to achieve conformance. A

compiler option must also be set to ensure that the operation of the compiler is consistent with the interface when the

project is built.

3.1 Background - The Desire for Portable Code

All programmers want to write portable source code.

Portability means that the same source code can be compiled and run in a different execution environment than that

for which it was written. Rarely can code be one hundred percent portable, but the more tolerant it is to change, the

less time and effort it takes to have it running in a new environment.

Embedded engineers typically think of code portability as being across target devices, but this is only part of the

situation. The same code could be compiled for the same target but with a different compiler. Differences between

those compilers might lead to the code failing at compile time or runtime, so this must be considered as well.

You can only write code for one target device and only use one brand of compiler; but if there is no regulation of the

compiler’s operation, simply updating your compiler version can change your code’s behavior.

Code must be portable across targets, tools, and time to be truly flexible.

Clearly, this portability cannot be achieved by the programmer alone, since the compiler vendors can base their

products on different technologies, implement different features and code syntax, or improve the way their product

works. Many a great compiler optimization has broken many an unsuspecting project.

Standards for the C language have been developed to ensure that change is managed and code is more portable.

The American National Standards Institute (ANSI) publishes standards for many disciplines, including programming

languages. The ANSI C Standard is a universally adopted standard for the C programming language.

3.1.1 The ANSI Standard

The ANSI C Standard has to reconcile two opposing goals: freedom for compilers vendors to target new devices and

improve code generation, with the known functional operation of source code for programmers. If both goals can be

met, source code can be made portable.

The standard is implemented as a set of rules which detail not only the syntax that a conforming C program must

follow, but the semantic rules by which that program will be interpreted. Thus, for a compiler to conform to the

standard, it must ensure that a conforming C program functions as described by the standard.

The standard describes implementation, the set of tools and the runtime environment on which the code will run. If

any of these change, for example, you build for, and run on, a different target device, or if you update the version of

the compiler you use to build, then you are using a different implementation.

The standard uses the term behavior to mean the external appearance or action of the program. It has nothing to do

with how a program is encoded.

Since the standard is trying to achieve goals that could be construed as conflicting, some specifications appear

somewhat vague. For example, the standard states that an int type must be able to hold at least a 16-bit value, but

it does not go as far as saying what the size of an int actually is; and the action of right-shifting a signed integer can

produce different results on different implementations; yet, these different results are still ANSI C compliant.

If the standard is too strict, device architectures cannot allow the compiler to conform (see following note). But, if it is

too weak, programmers would see wildly differing results within different compilers and architectures, and the

standard would lose its effectiveness.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 12

Note: For example, the mid-range PIC

®

microcontrollers do not have a data stack. Because a compiler targeting this

device cannot implement recursion, it (strictly speaking) cannot conform to the ANSI C Standard. This example

illustrates a situation in which the standard is too strict for mid-range devices and tools.

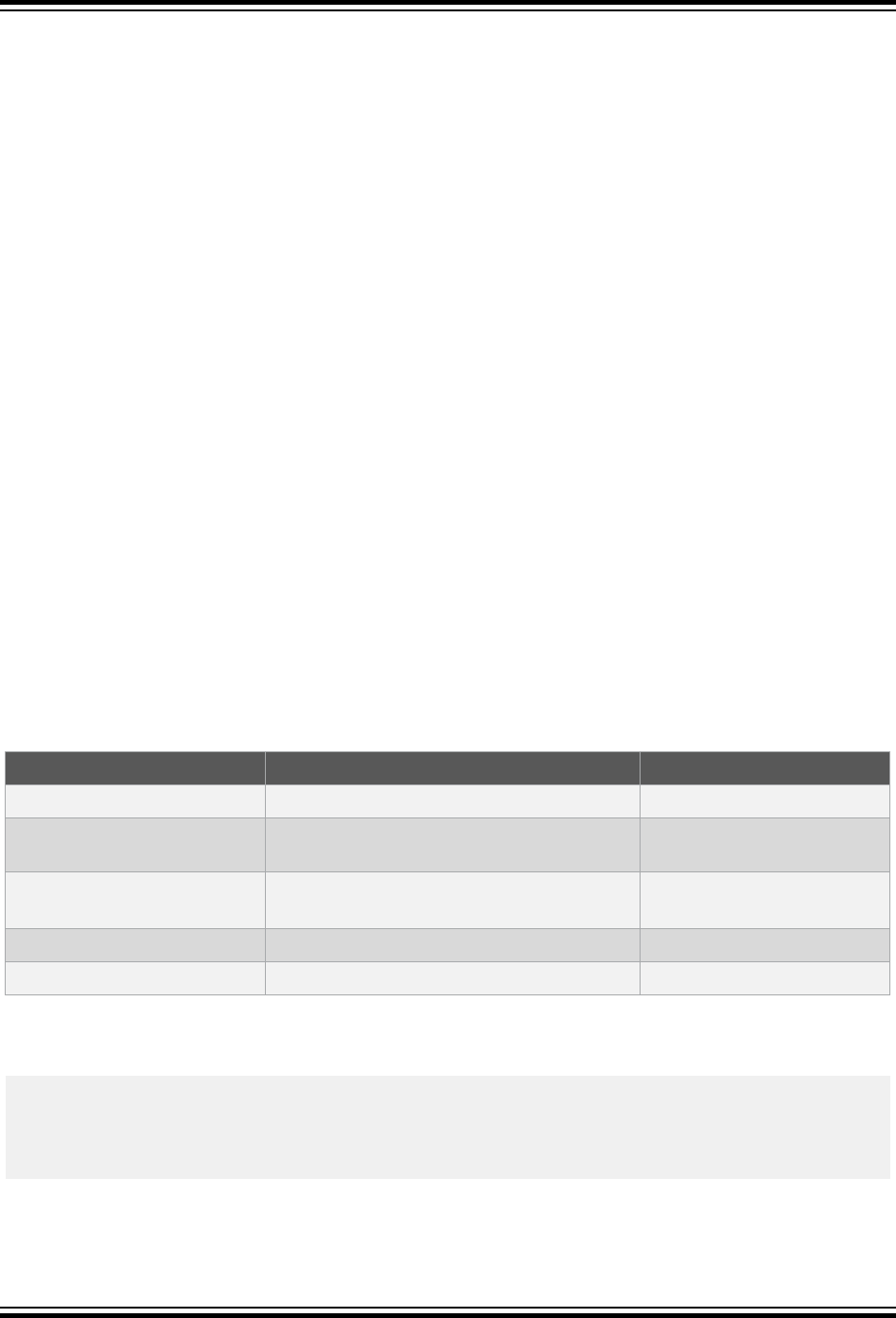

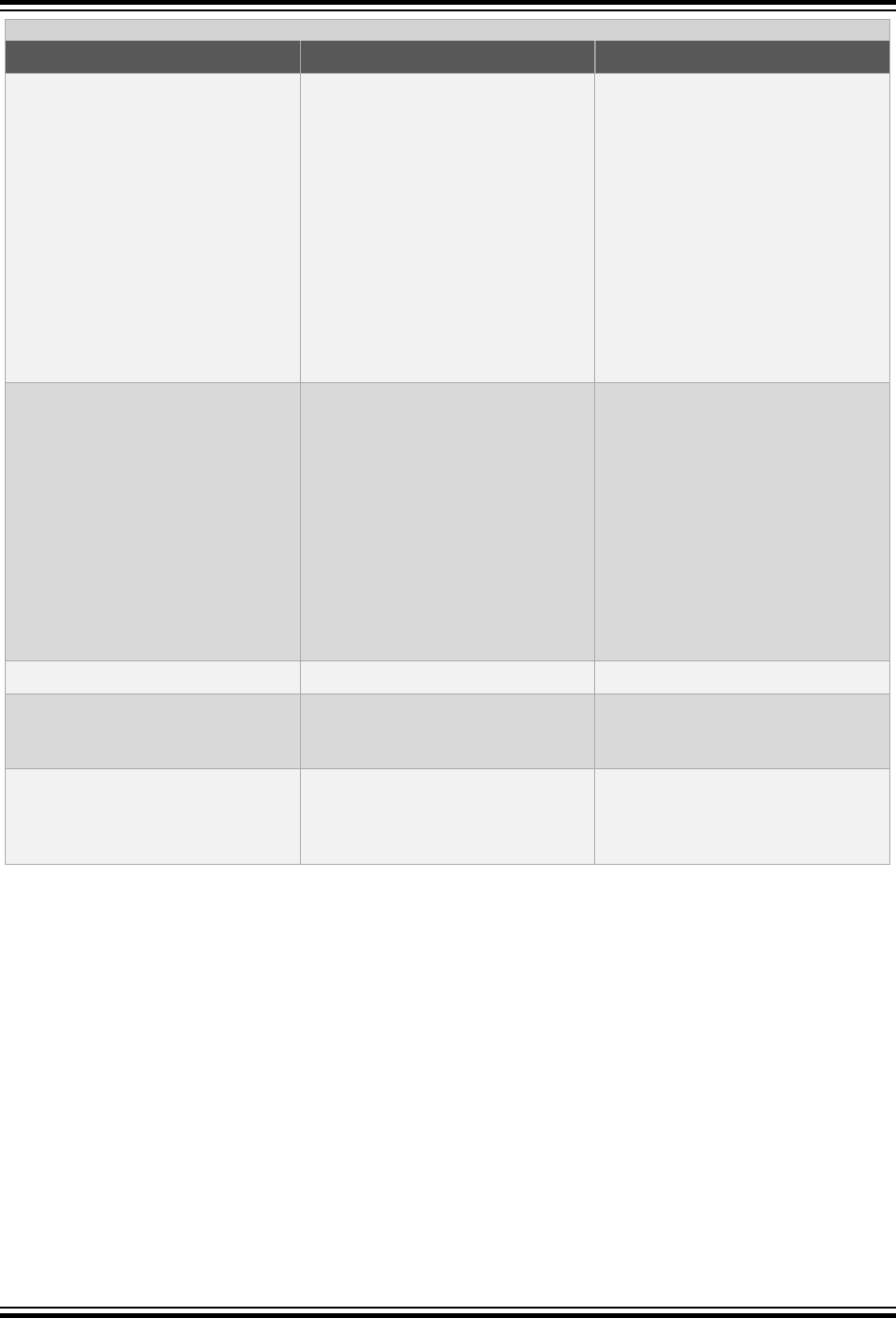

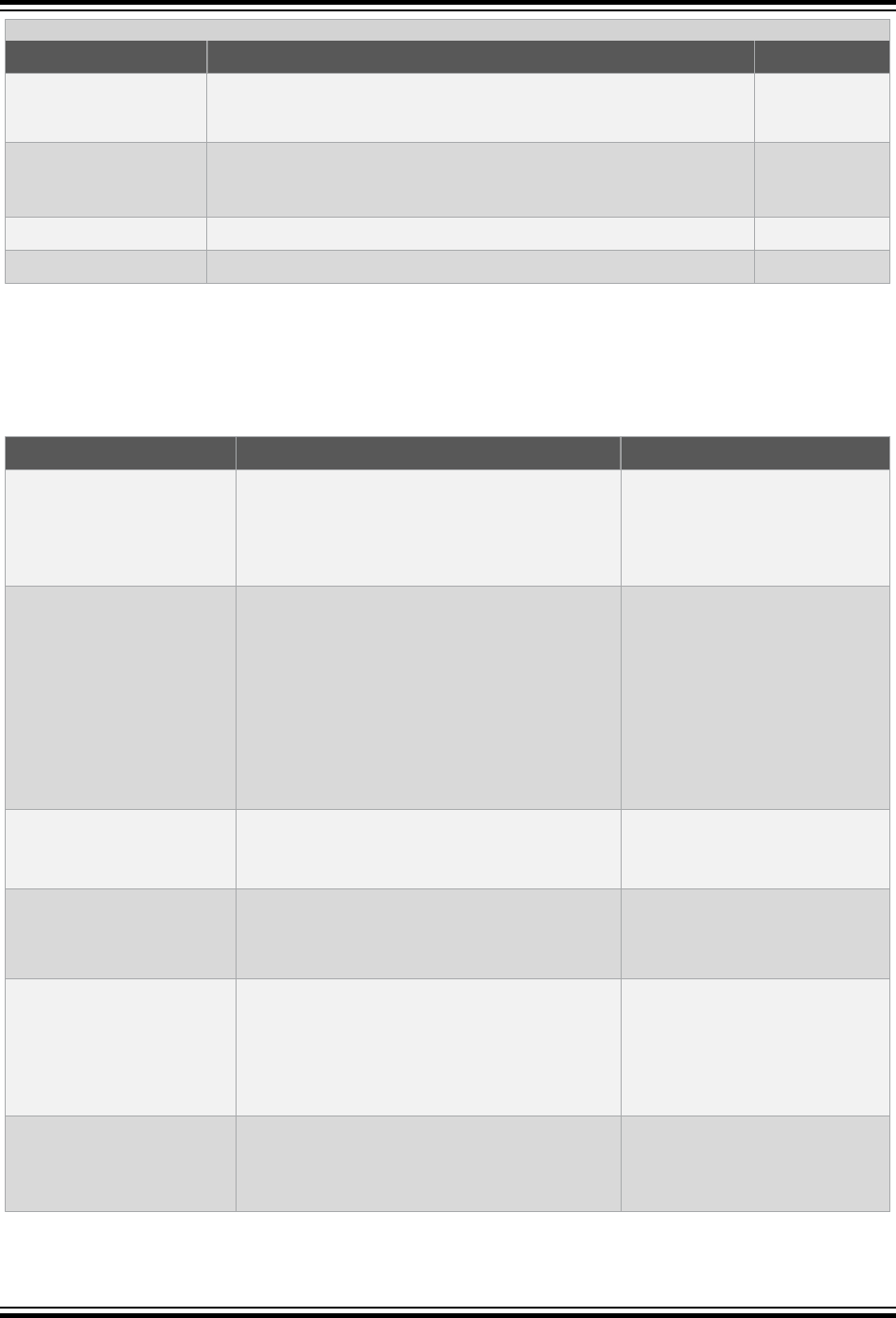

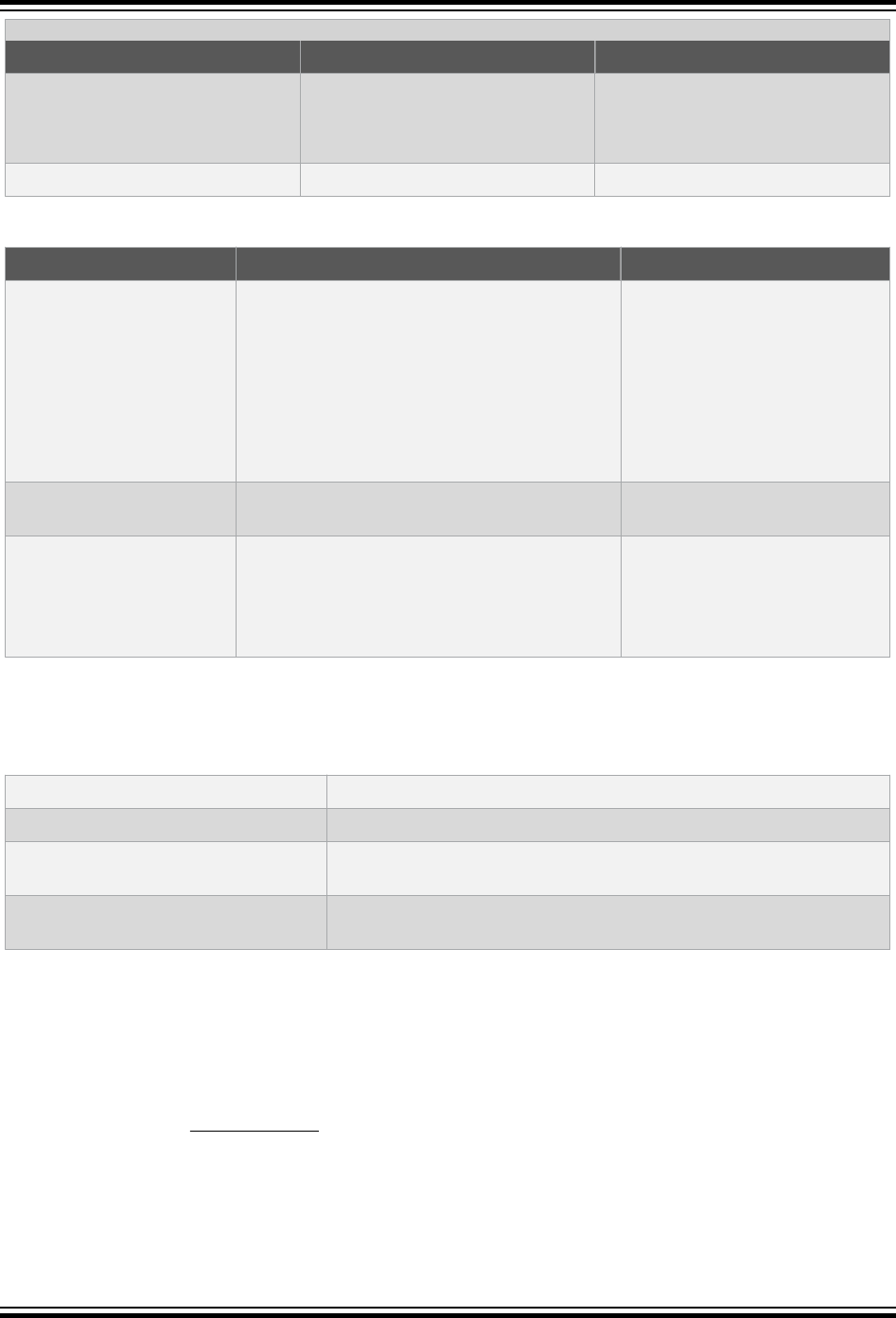

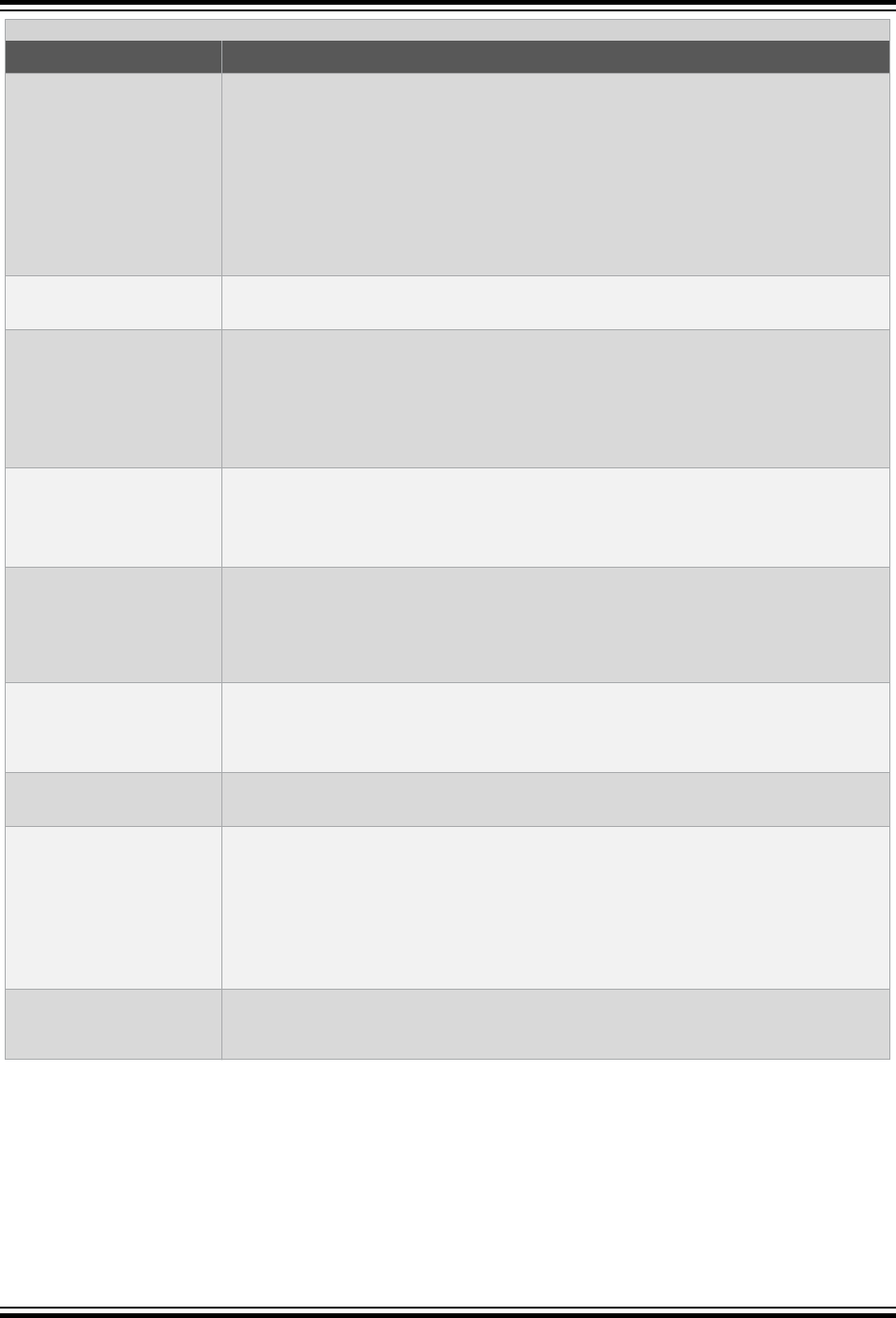

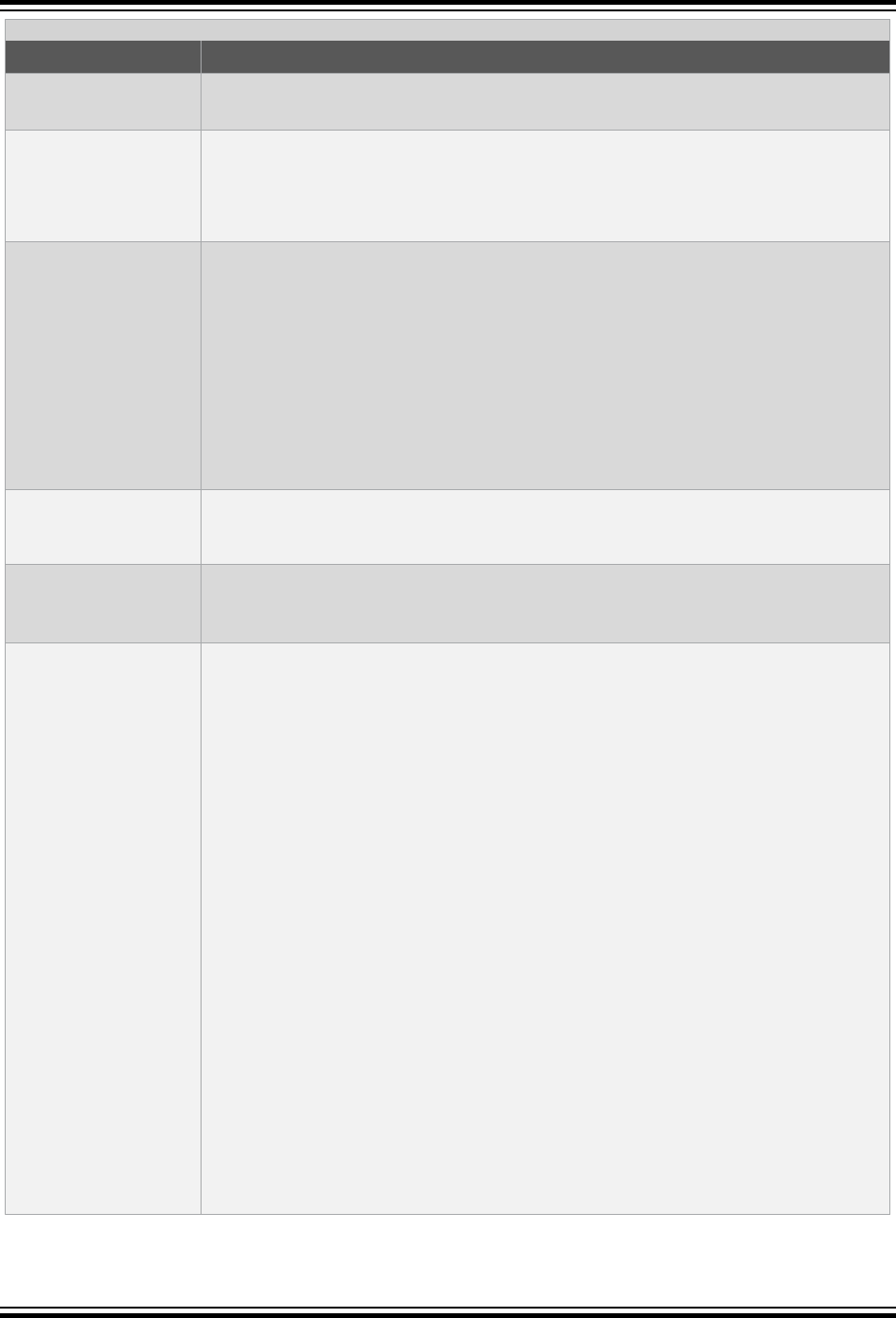

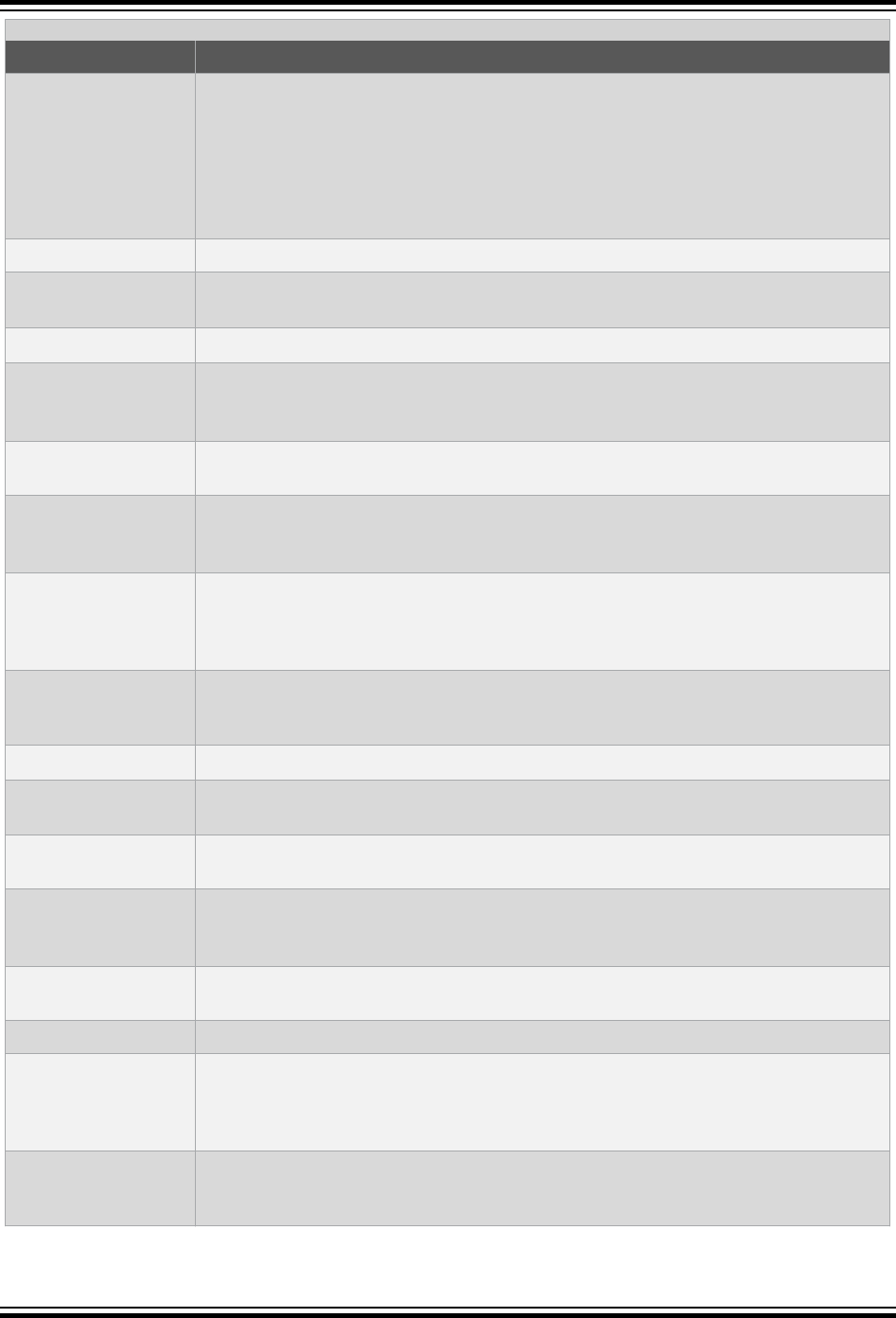

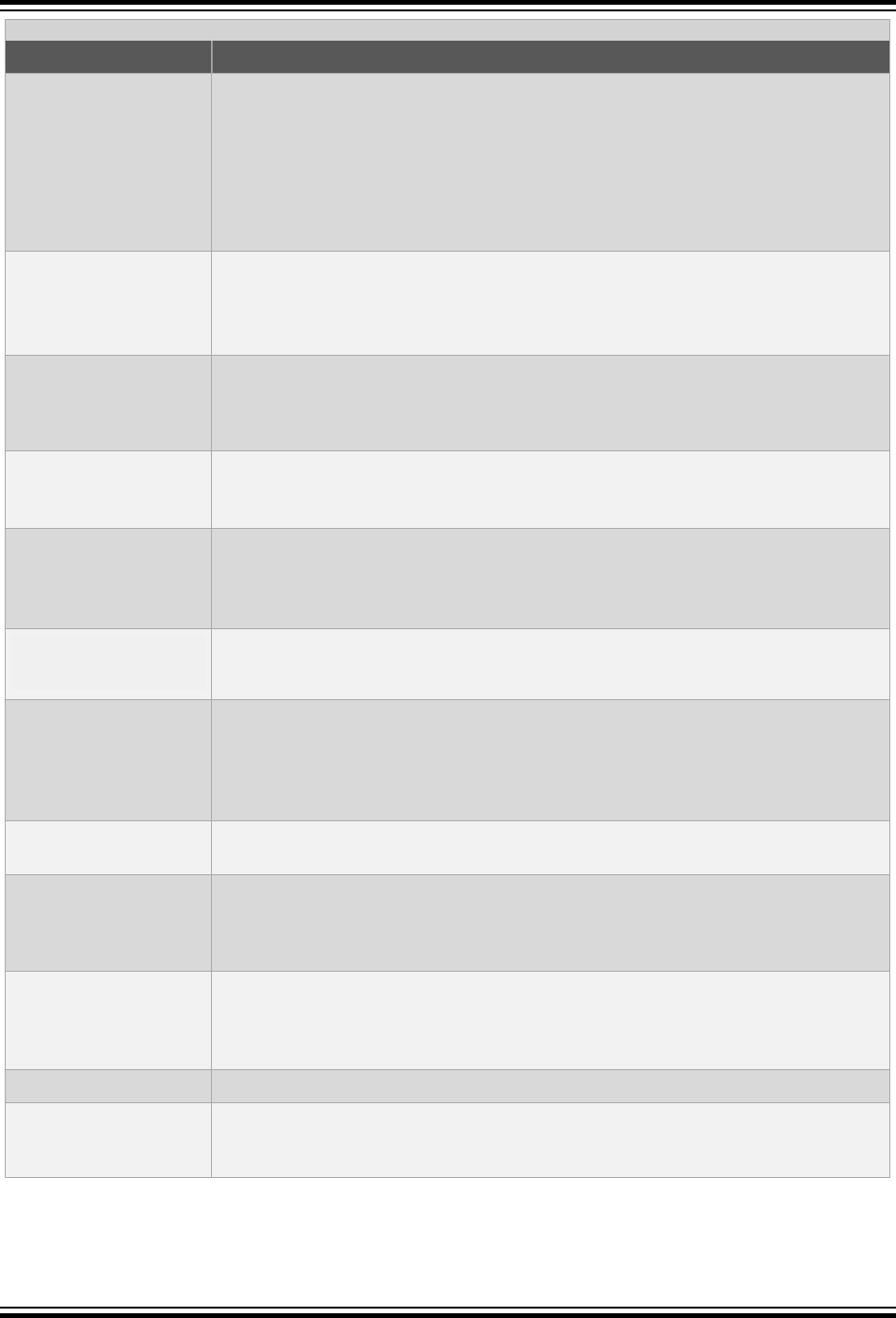

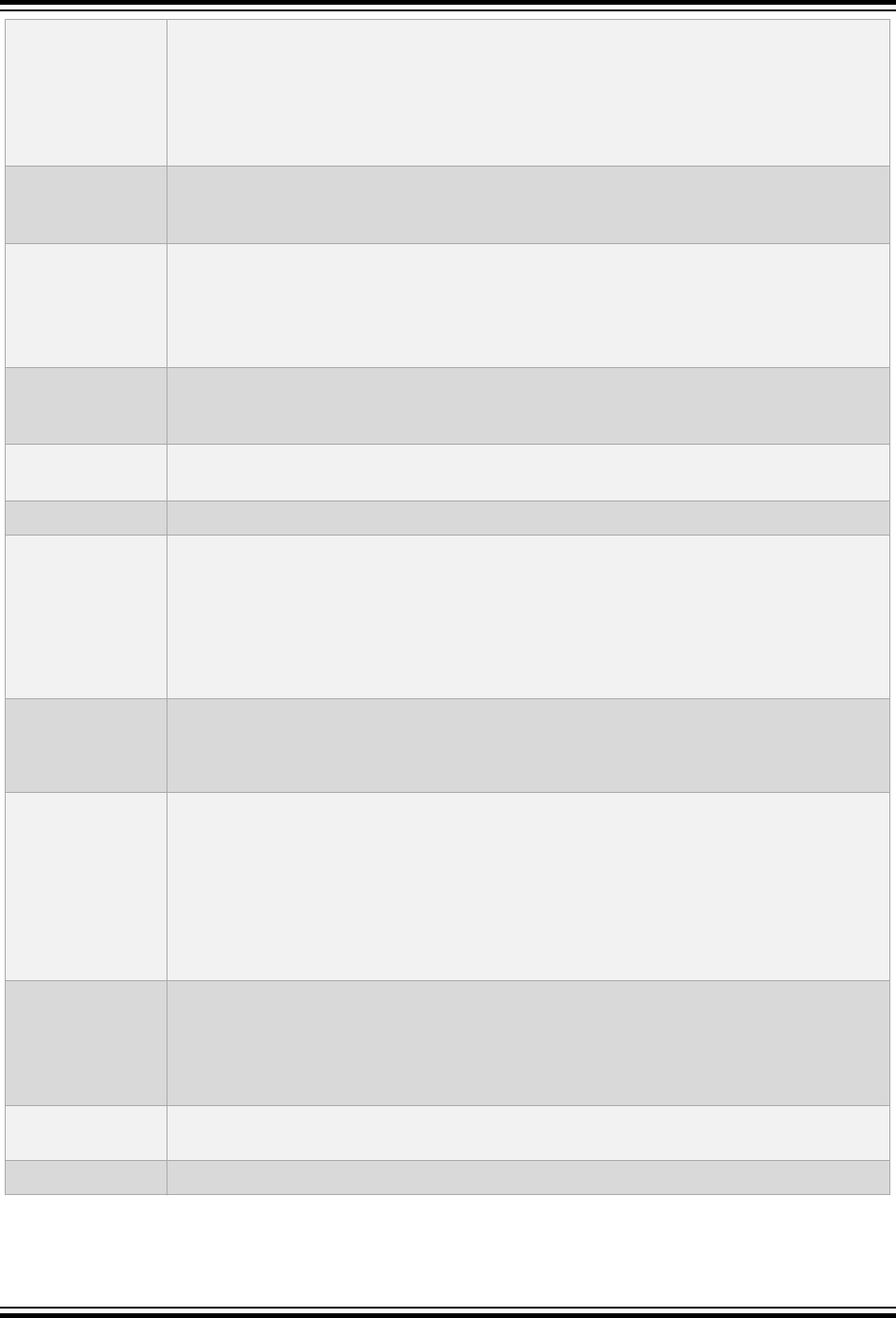

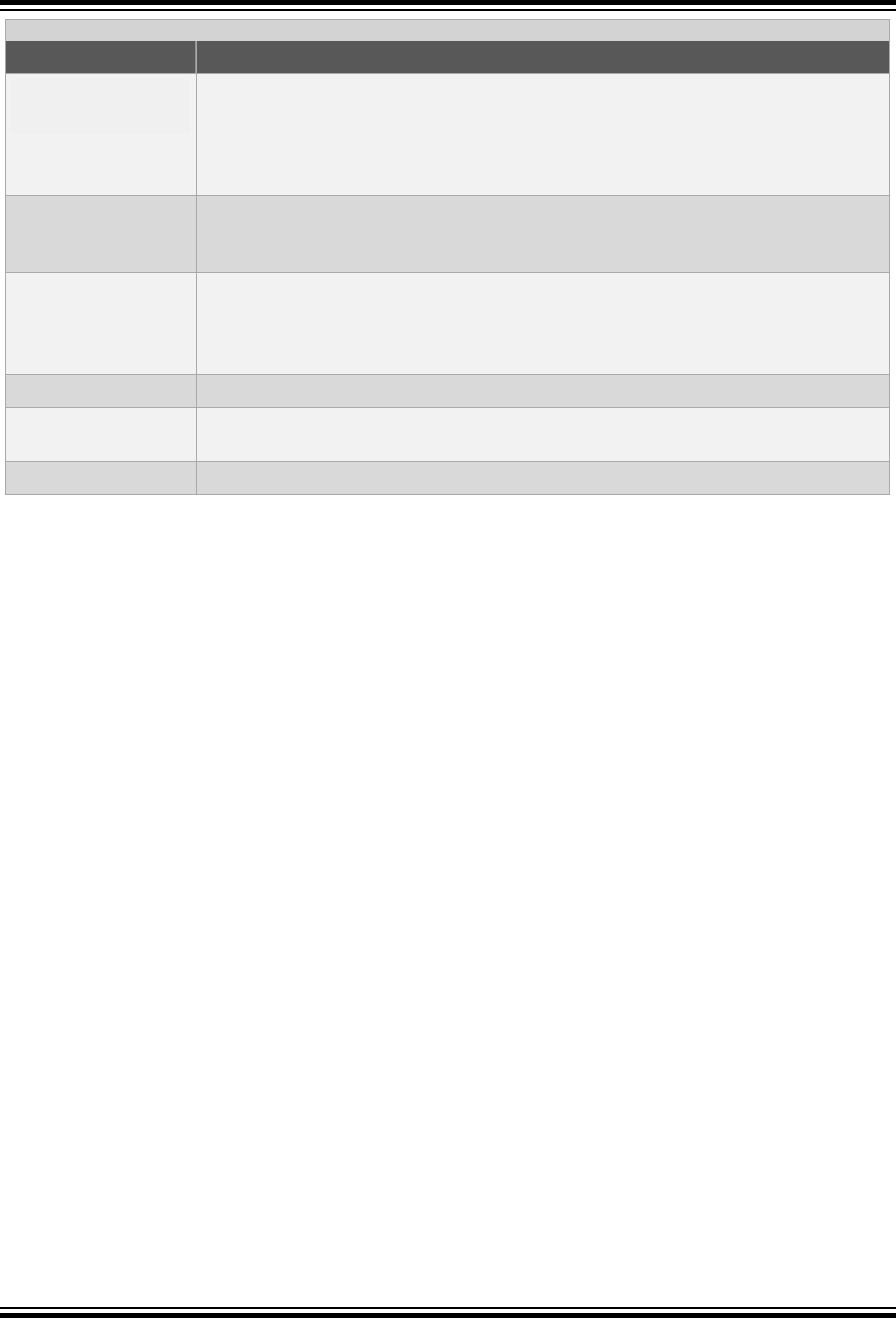

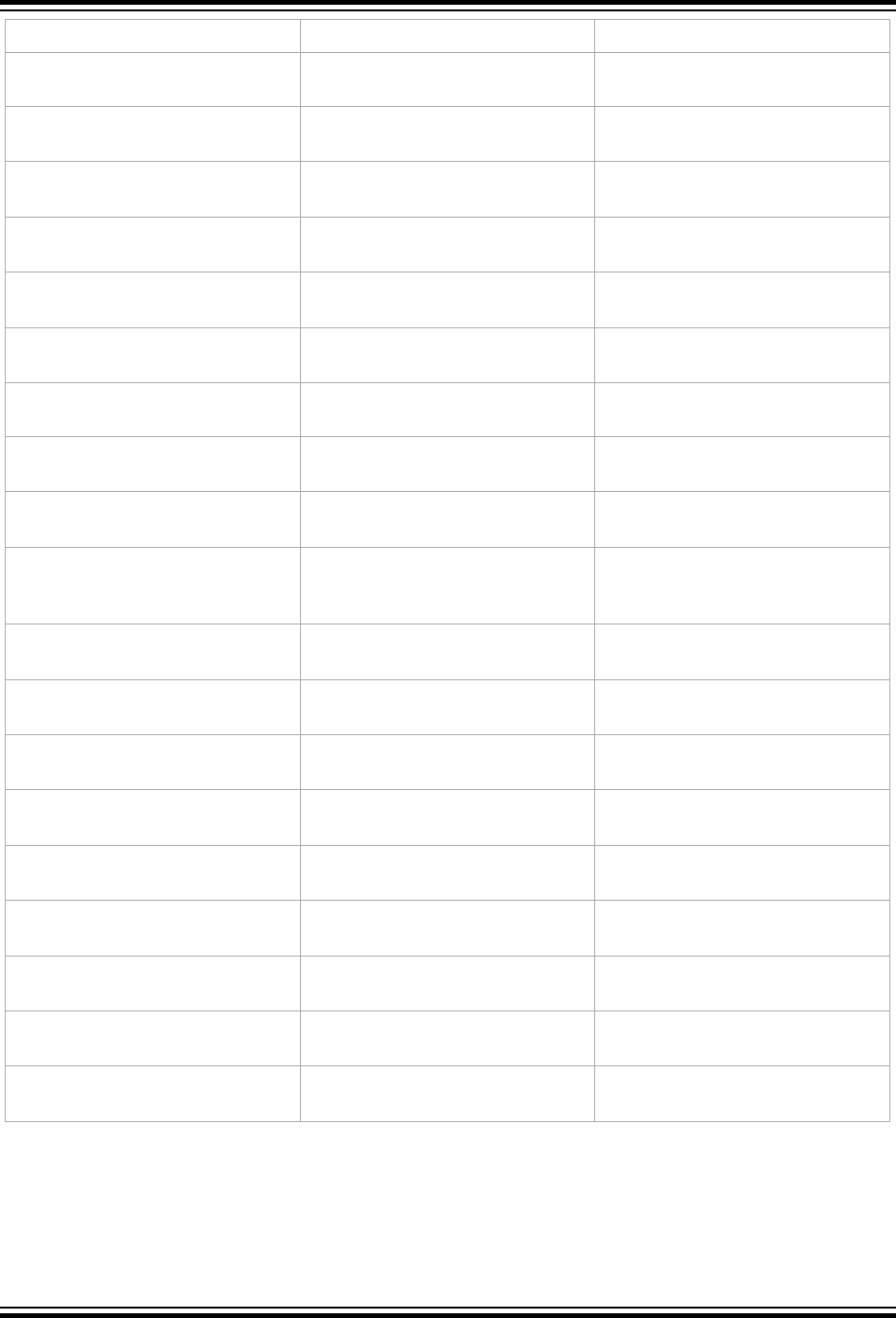

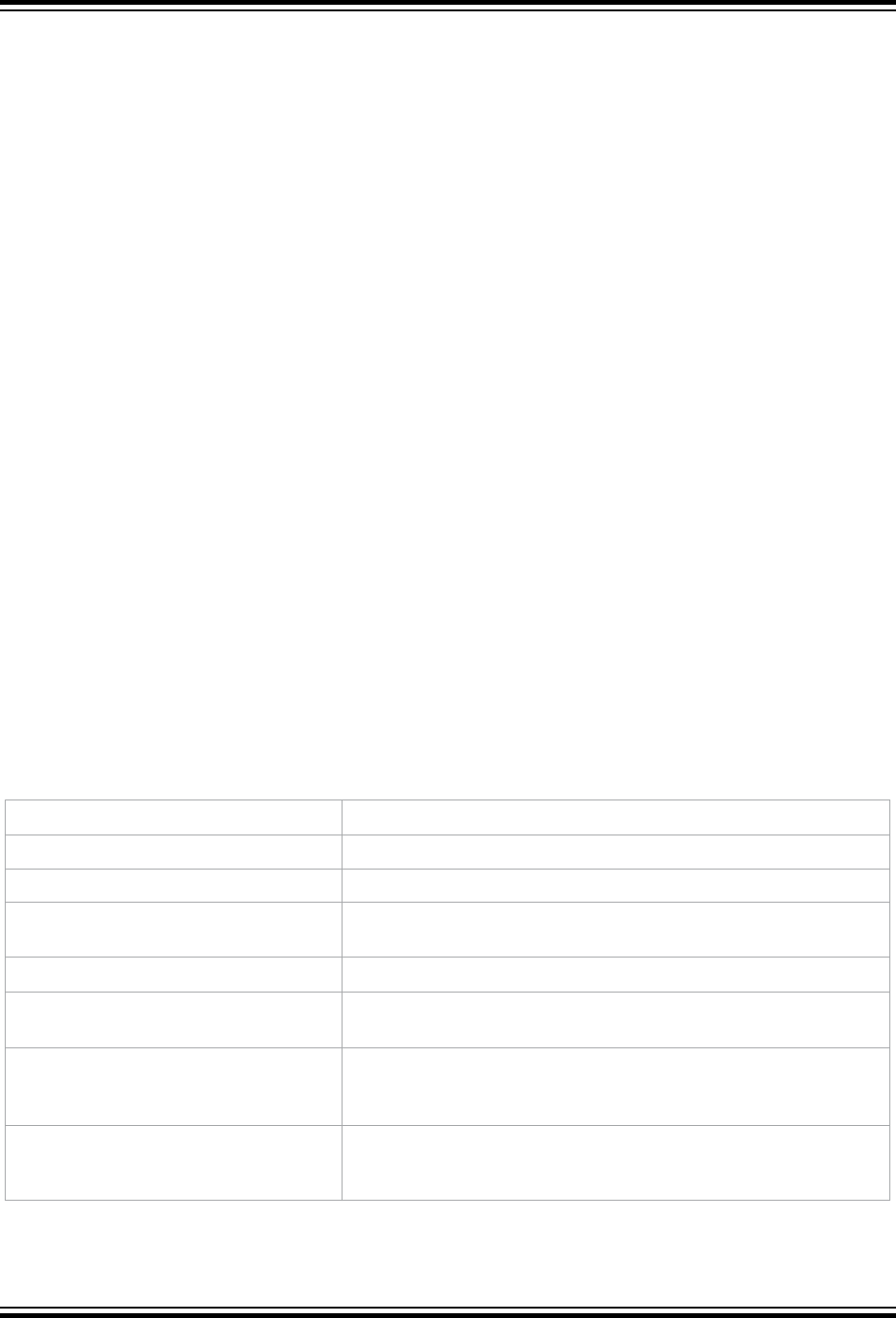

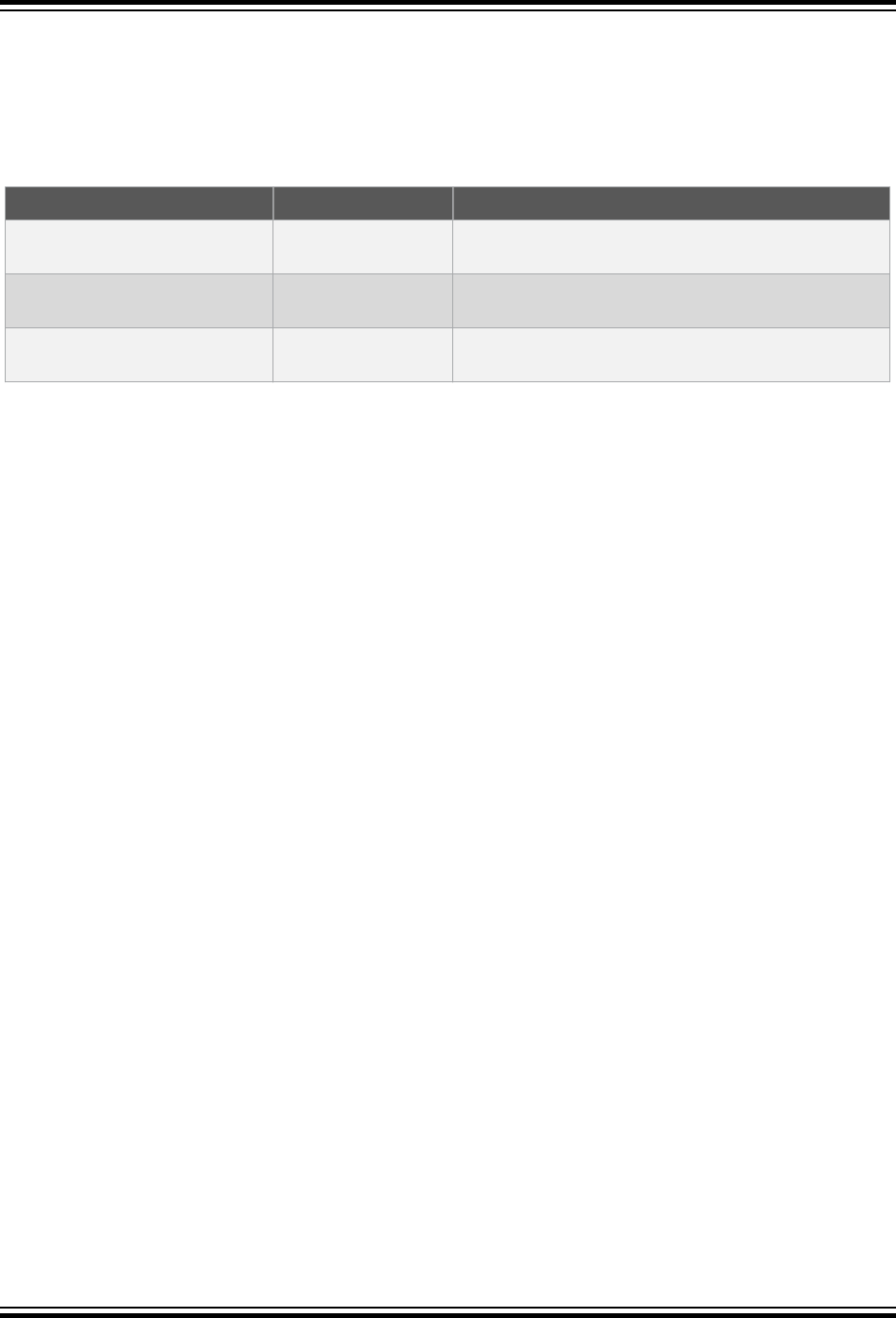

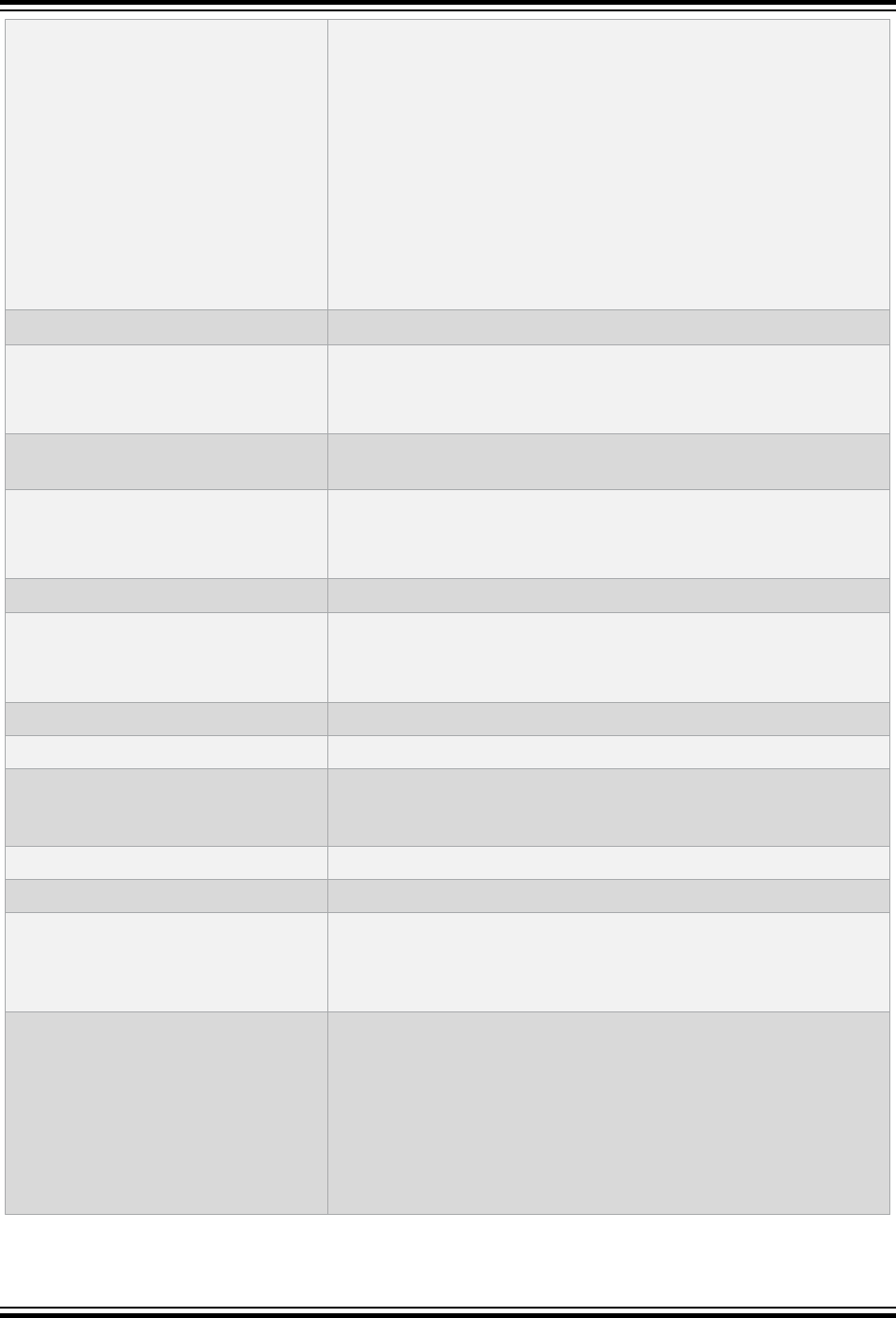

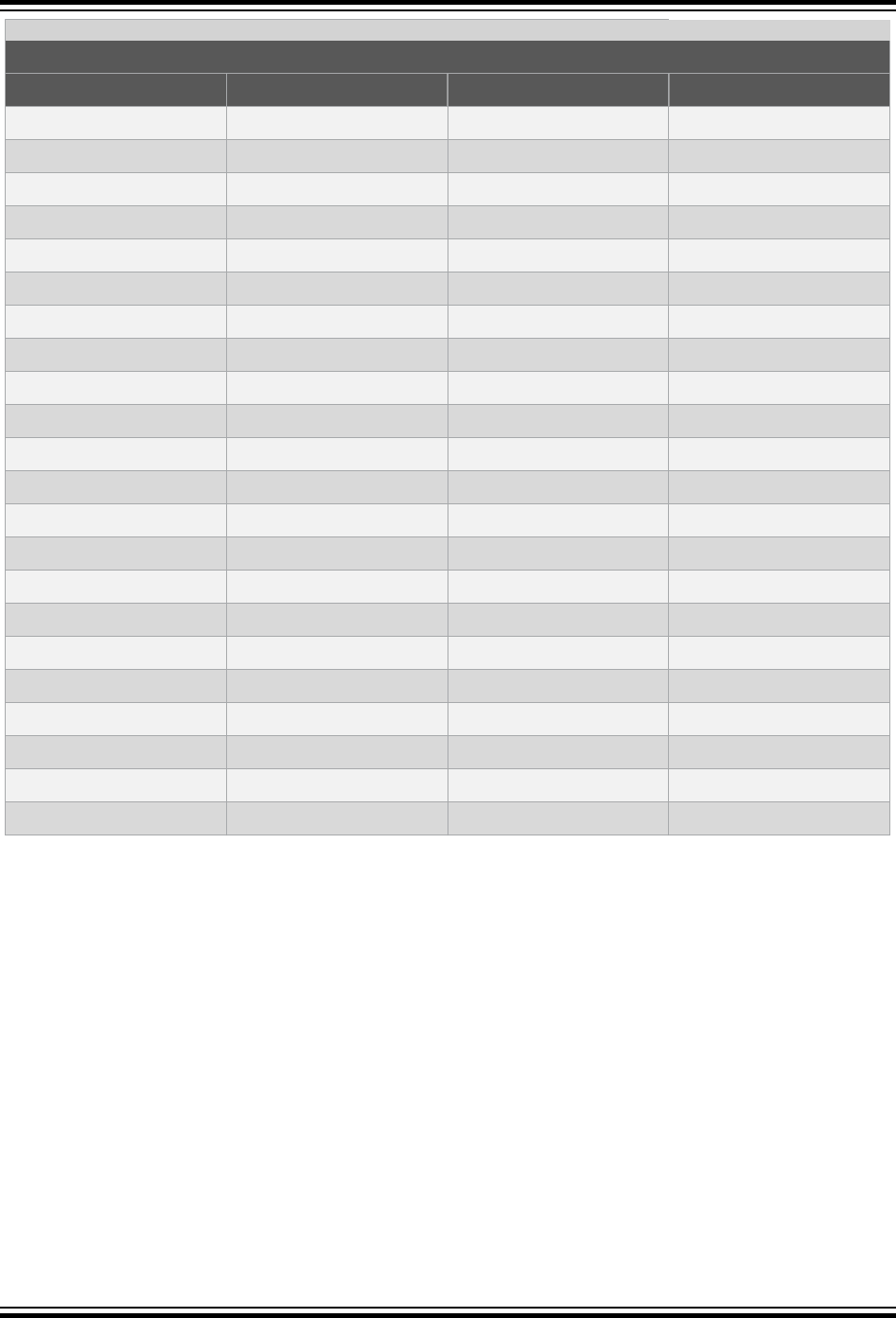

The standard organizes source code whose behavior is not fully defined into groups that include the following

behaviors:

Implementation-defined behavior This is unspecified behavior in which each implementation

documents how the choice is made.

Unspecified behavior The standard provides two or more possibilities and imposes no

further requirements on which possibility is chosen in any

particular instance.

Undefined behavior This is behavior for which the standard imposes no requirements.

Code that strictly conforms to the standard does not produce output that is dependent on any unspecified, undefined,

or implementation-defined behavior. The size of an int, which was used as an example earlier, falls into the

category of behavior that is defined by implementation. That is to say, the size of an int is defined by which compiler

is being used, how that compiler is being used, and the device that is being targeted.

All the MPLAB XC compilers conform to the ANSI X3.159-1989 Standard for programming languages (with the

exception of the MPLAB XC8 compiler’s inability to allow recursion, as mentioned in the footnote). This is commonly

called the C89 Standard. Some features from the later standard, C99, are also supported.

For freestanding implementations (or for what are typically call embedded applications), the standard allows non-

standard extensions to the language, but obviously does not enforce how they are specified or how they work. When

working so closely to the device hardware, a programmer needs a means of specifying device setup and interrupts,

as well as utilizing the often complex world of small-device memory architectures. This cannot be offered by the

standard in a consistent way.

While the ANSI C Standard provides a mutual understanding for programmers and compiler vendors, programmers

need to consider the implementation-defined behavior of their tools and the probability that they may need to use

extensions to the C language that are non-standard. Both of these circumstances can have an impact on code

portability.

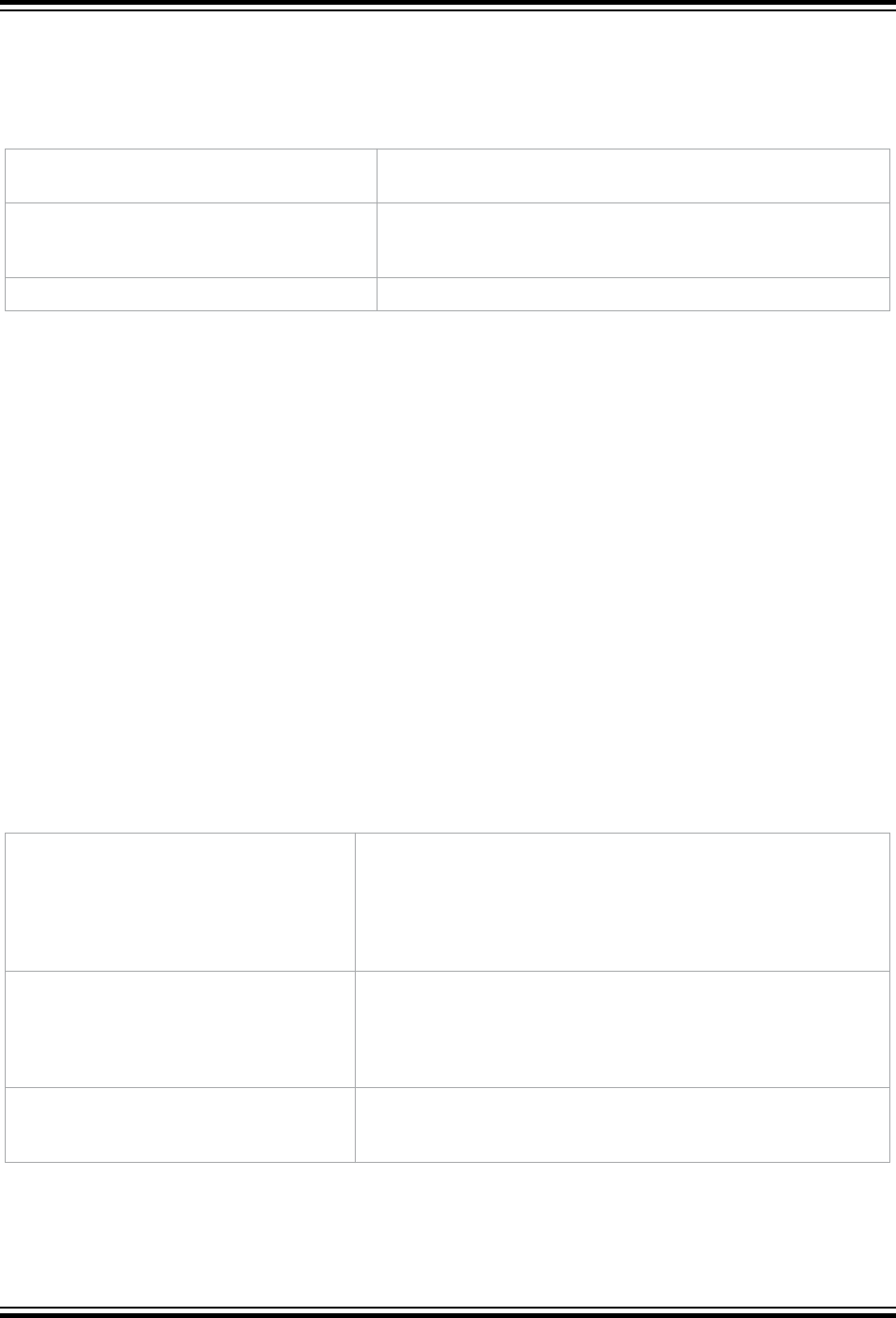

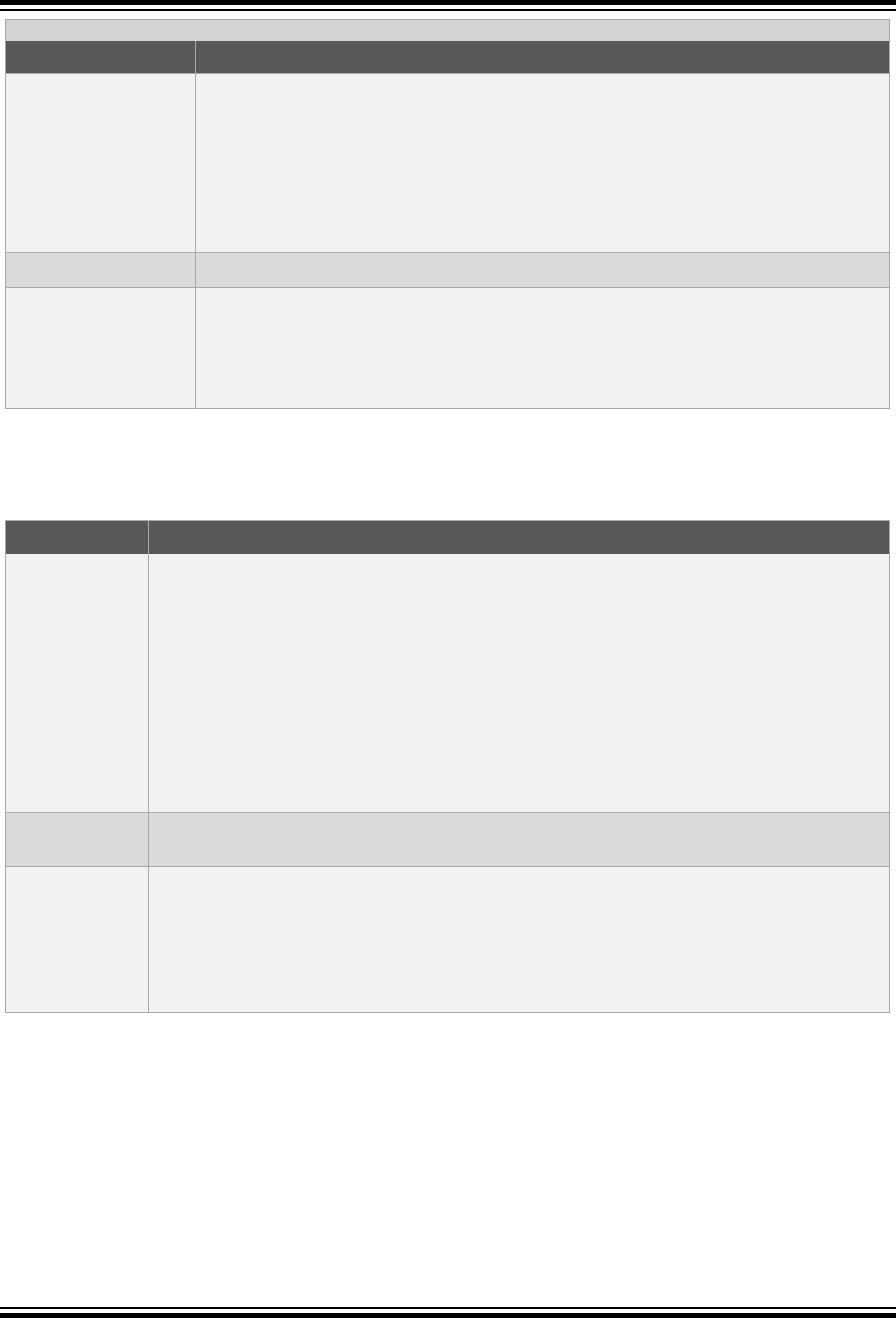

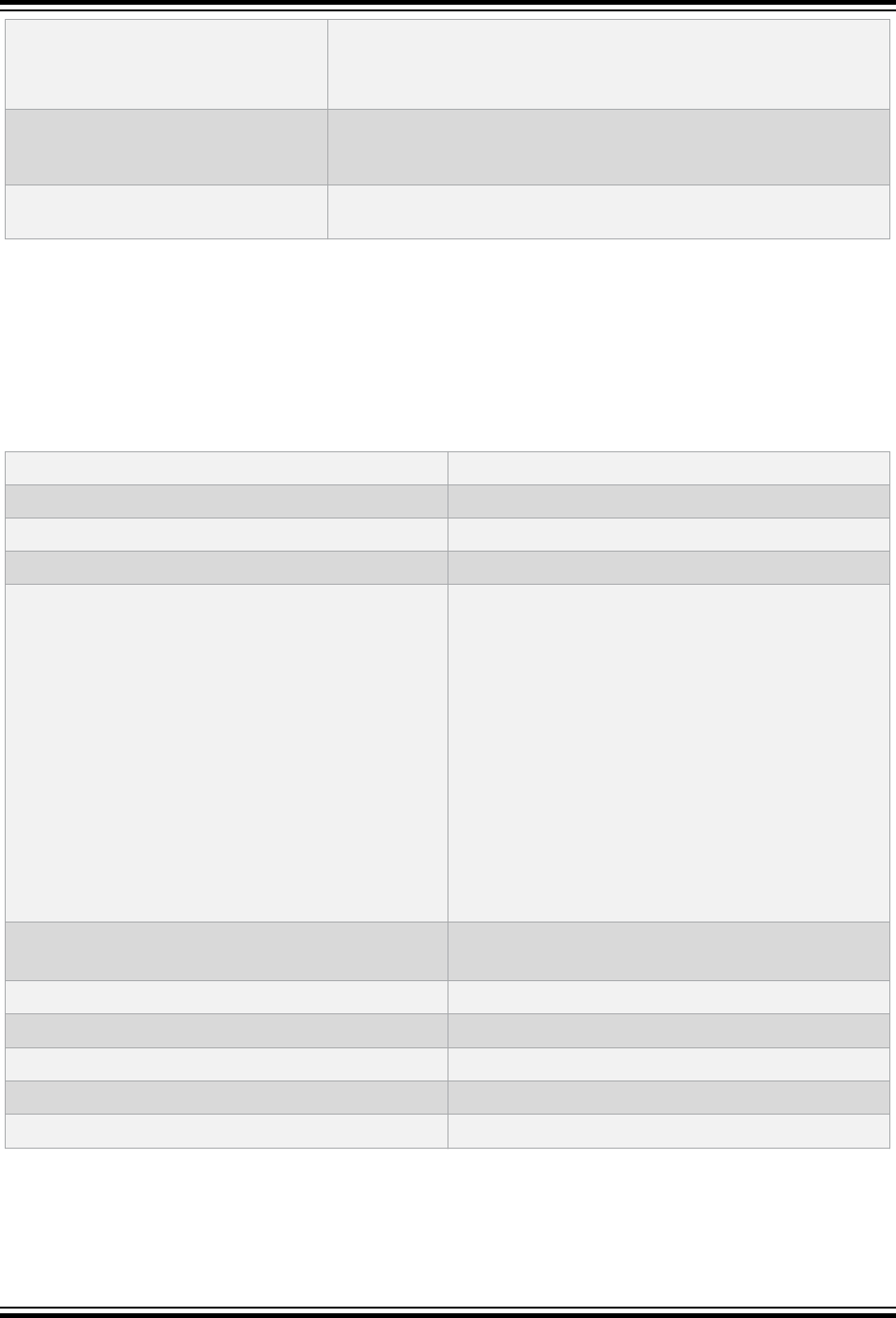

3.1.2 The Common C Interface

The Common C Interface (CCI) supplements the ANSI C Standard and makes it easier for programmers to achieve

consistent outcomes on all Microchip devices when using any of the MPLAB XC C compilers.

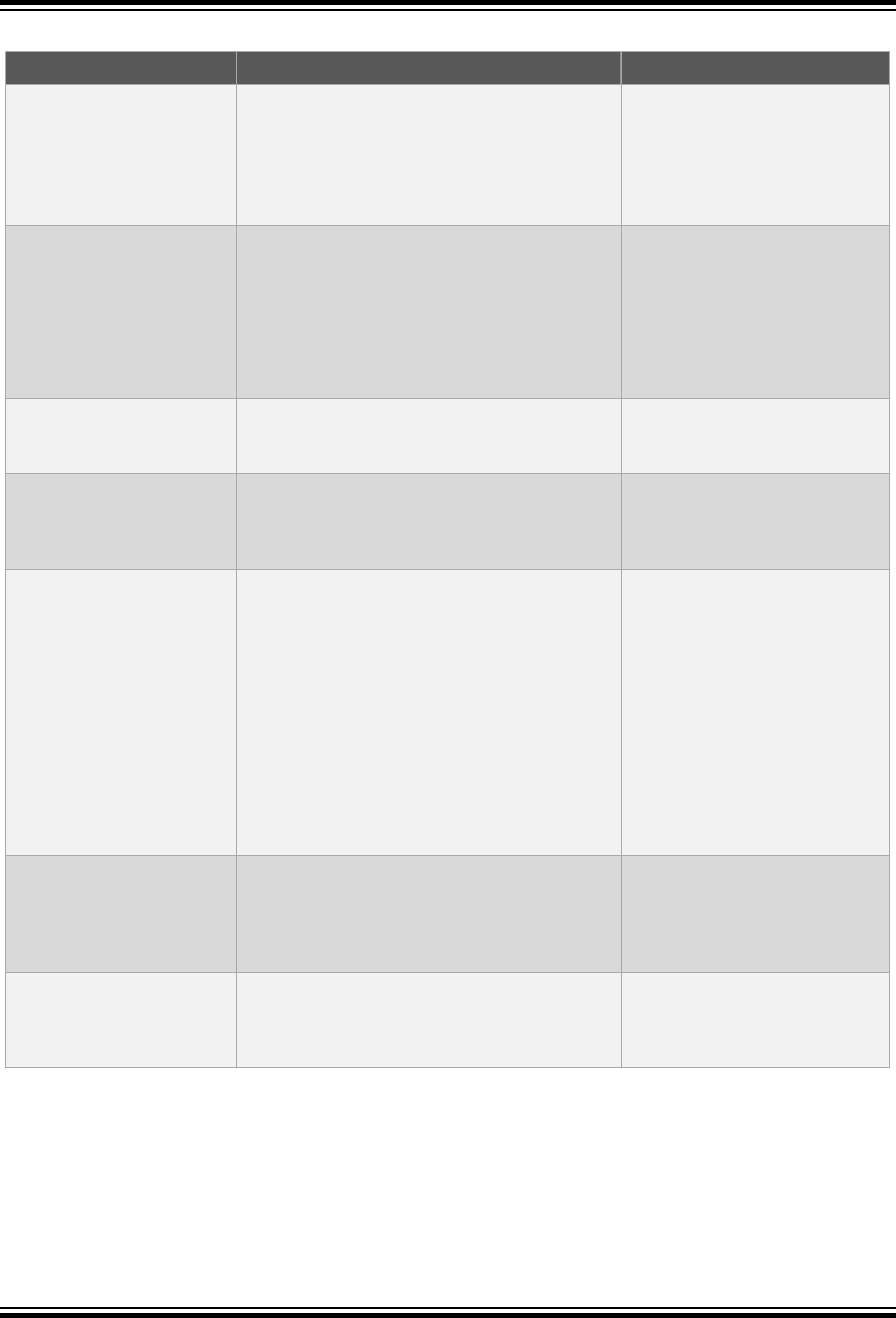

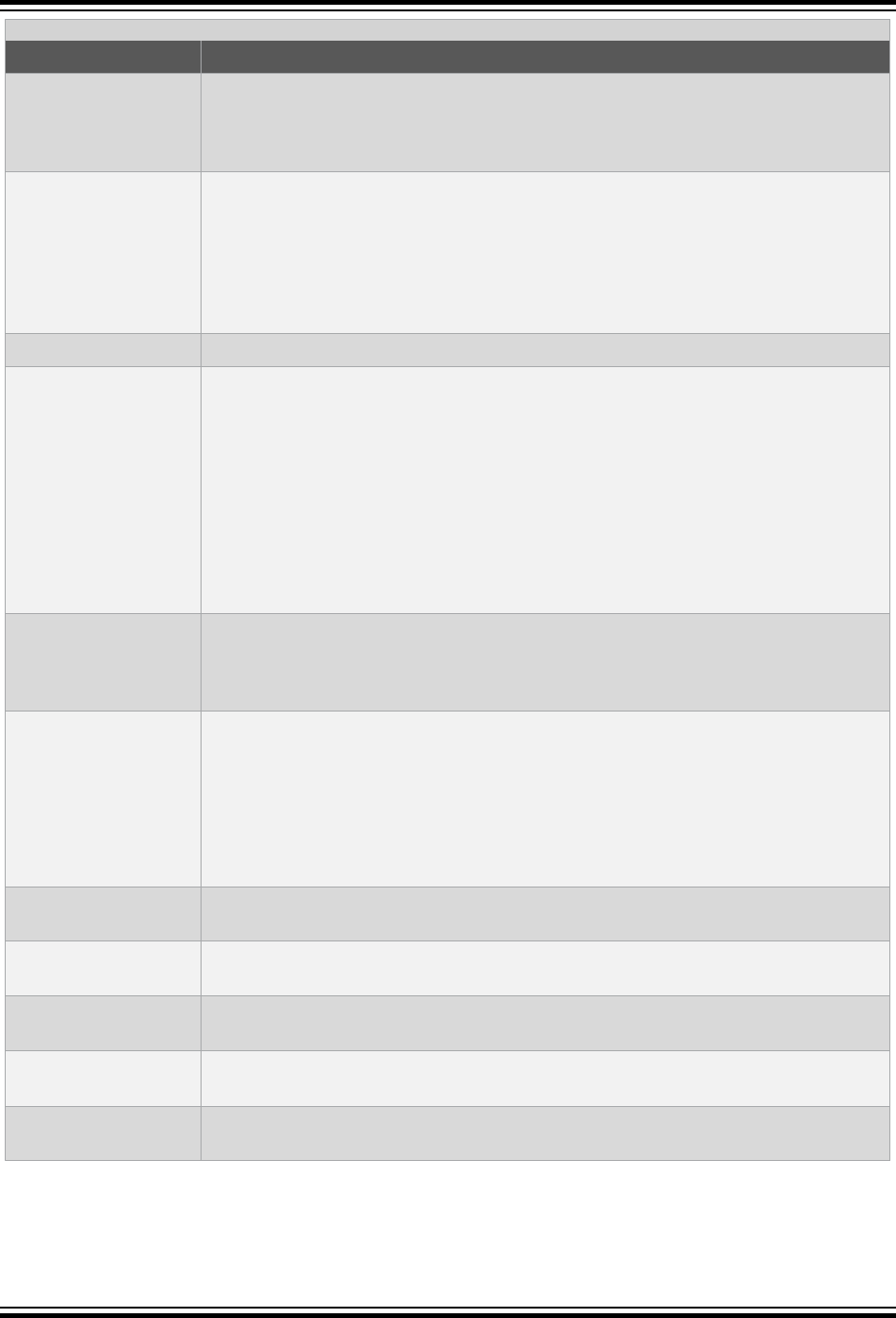

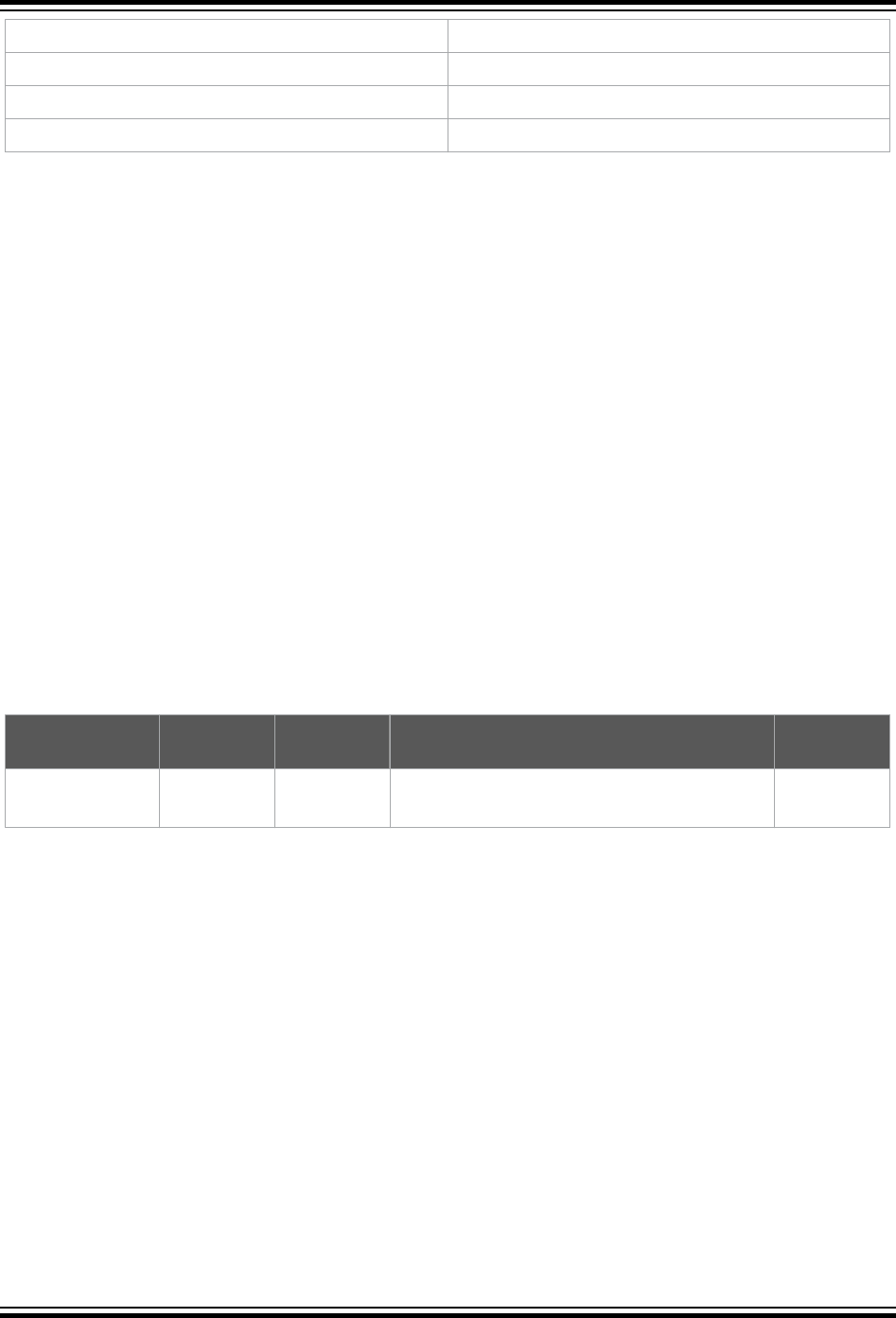

It delivers the following improvements, all designed with portability in mind.

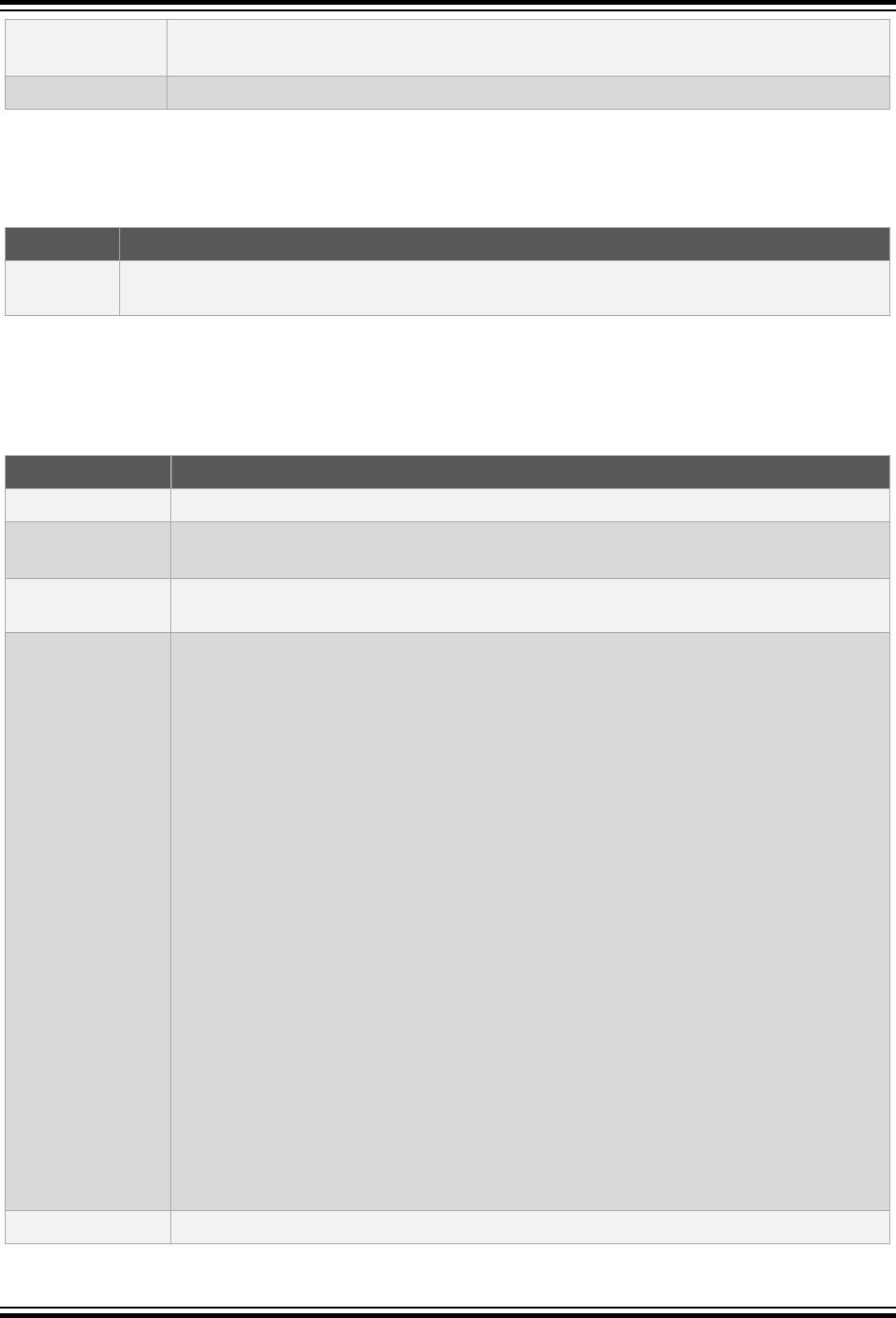

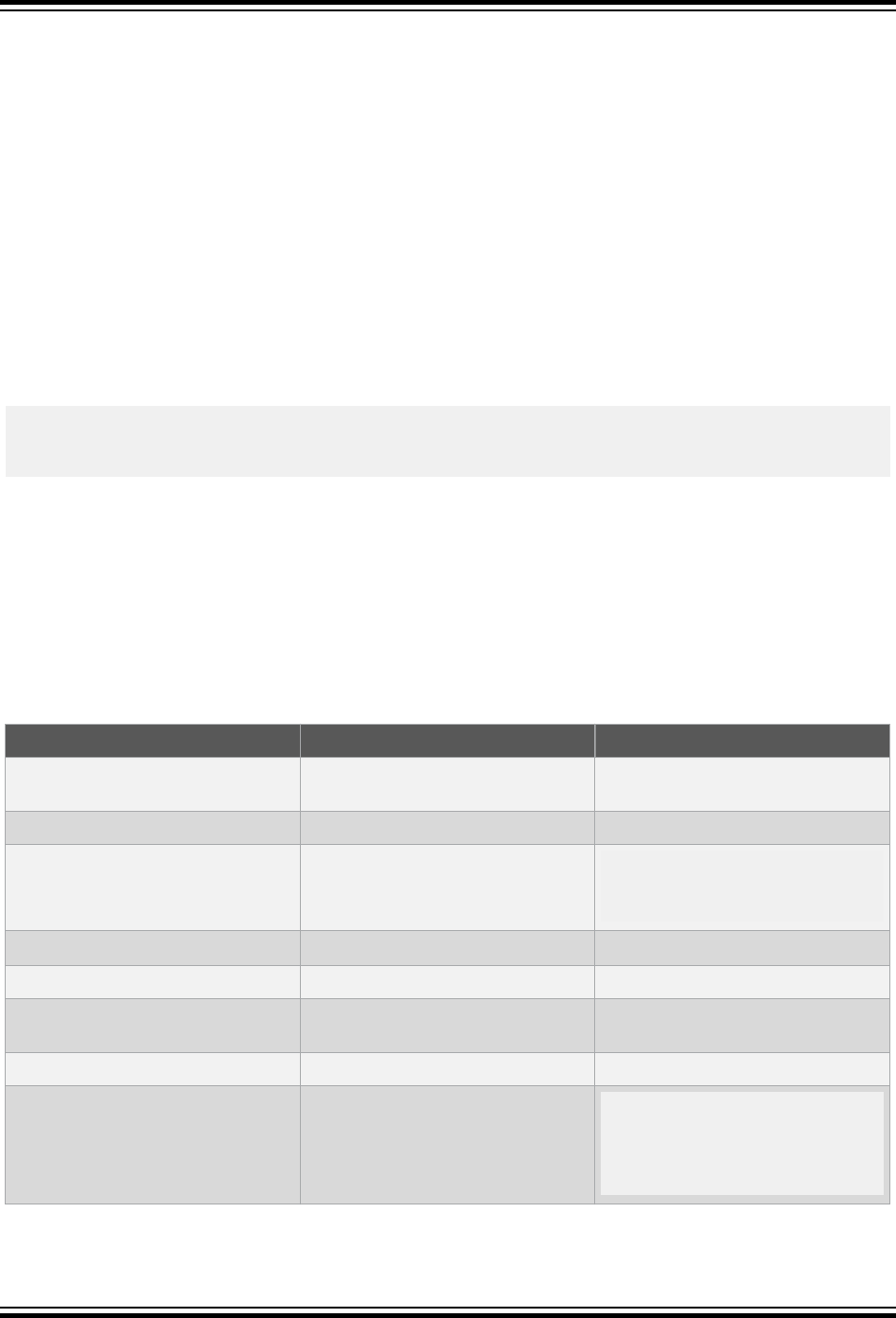

Refinement of the ANSI C Standard The CCI documents specific behavior for some code in which actions

are implementation-defined behavior under the ANSI C Standard.

For example, the result of right-shifting a signed integer is fully

defined by the CCI. Note that many implementation-defined items

that closely couple with device characteristics, such as the size of an

int, are not defined by the CCI.

Consistent syntax for non-standard

extensions

The CCI non-standard extensions are mostly implemented using

keywords with a uniform syntax. They replace keywords, macros and

attributes that are the native compiler implementation. The

interpretation of the keyword can differ across each compiler, and

any arguments to the keywords can be device specific.

Coding guidelines The CCI can indicate advice on how code should be written so that it

can be ported to other devices or compilers. While you may choose

not to follow the advice, it will not conform to the CCI.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 13

3.2 Using the CCI

The CCI allows enhanced portability by refining implementation-defined behavior and standardizing the syntax for

extensions to the language.

The CCI is something you choose to follow and put into effect, thus it is relevant for new projects, although you can

choose to modify existing projects so they conform.

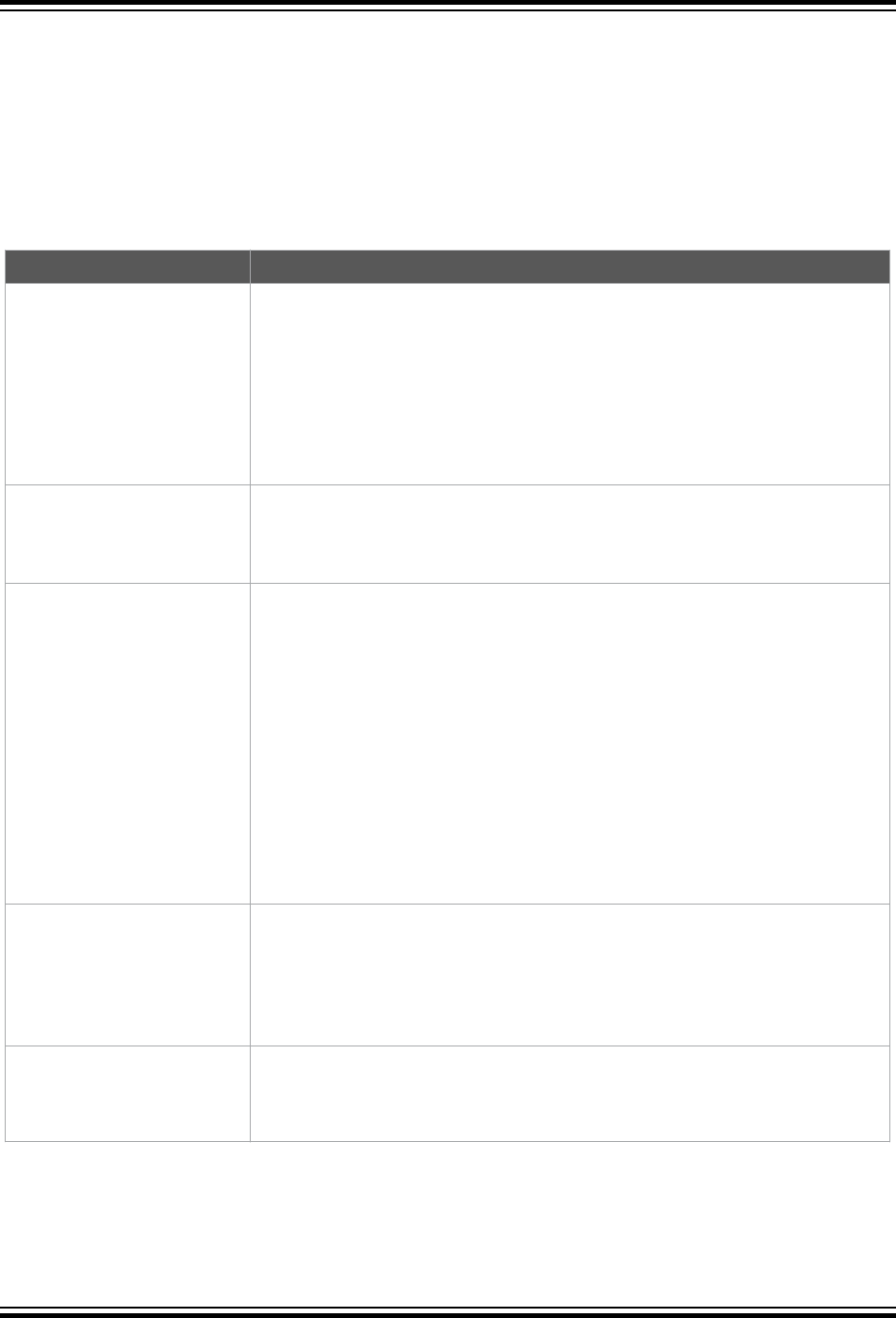

For your project to conform to the CCI, you must do the following things.

• Enable the CCI

Select the MPLAB X IDE widget

Use CCI Syntax in your project, or use the command-line option that is

equivalent.

• Include <xc.h> in every module

Some CCI features are only enabled if this header is seen by the compiler.

• Ensure ANSI compliance

Code that does not conform to the ANSI C Standard does not conform to the CCI.

• Observe refinements to ANSI by the CCI

Some ANSI implementation-defined behavior is defined explicitly by the CCI.

• Use the CCI extensions to the language

Use the CCI extensions rather than the native language extensions.

The next sections detail specific items associated with the CCI. These items are segregated into those that refine the

standard, those that deal with the ANSI C Standard extensions, and other miscellaneous compiler options and usage.

Guidelines are indicated with these items.

If any implementation-defined behavior or any non-standard extension is not discussed in this document, then it is not

part of the CCI. For example, GCC case ranges, label addresses and 24-bit short long types are not part of the

CCI. Programs which use these features do not conform to the CCI. The compiler may issue a warning or error to

indicate a non-CCI feature has been used and the CCI is enabled.

3.3 ANSI Standard Refinement

The following topics describe how the CCI refines the implementation-defined behaviors outlined in the ANSI C

Standard.

3.3.1 Source File Encoding

Under the CCI, a source file must be written using characters from the 7-bit ASCII set. Lines can be terminated using

a line feed (\n) or carriage return (\r) that is immediately followed by a line feed. Escaped characters can be used

in character constants or string literals to represent extended characters that are not in the basic character set.

Example

The following shows a string constant being defined that uses escaped characters.

const char myName[] = "Bj\370rk\n";

Differences

All compilers have used this character set.

Migration to the CCI

No action required.

3.3.2 The Prototype for main

The prototype for the main() function is:

int main(void);

Example

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 14

The following shows an example of how main() might be defined:

int main(void)

{

while(1)

process();

}

Differences

The 8-bit compilers used a void return type for this function.

Migration to the CCI

Each program has one definition for the main() function. Confirm the return type for main() in all projects

previously compiled for 8-bit targets.

3.3.3 Header File Specification

Header file specifications that use directory separators do not conform to the CCI.

Example

The following example shows two conforming include directives.

#include <usb_main.h>

#include "global.h"

Differences

Header file specifications that use directory separators have been allowed in previous versions of all compilers.

Compatibility problems arose when Windows-style separators “\” were used and the code was compiled under other

host operating systems. Under the CCI, no directory separators should be used.

Migration to the CCI

Any #include directives that use directory separators in the header file specifications should be changed. Remove

all but the header file name in the directive. Add the directory path to the compiler’s include search path or MPLAB X

IDE equivalent. This will force the compiler to search the directories specified with this option.

For example, the following code:

#include <inc/lcd.h>

should be changed to:

#include <lcd.h>

and the path to the inc directory added to the compiler’s header search path in your MPLAB X IDE project

properties, or on the command-line as follows:

-Ilcd

3.3.4 Include Search Paths

When you include a header file under the CCI, the file should be discoverable in the paths searched by the compiler

that are detailed below.

Header files specified in angle bracket delimiters < > should be discoverable in the search paths that are specified

by -I options (or the equivalent MPLAB X IDE option), or in the standard compiler include directories. The -I

options are searched in the order in which they are specified.

Header files specified in quote characters " " should be discoverable in the current working directory or in the same

directories that are searched when the header files are specified in angle bracket delimiters (as above). In the case of

an MPLAB X project, the current working directory is the directory in which the C source file is located. If

unsuccessful, the search paths should be to the same directories searched when the header file is specified in angle

bracket delimiters.

Any other options to specify search paths for header files do not conform to the CCI.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 15

Example

If including a header file, as in the following directive:

#include "myGlobals.h"

the header file should be locatable in the current working directory, or the paths specified by any -I options, or the

standard compiler directories. A header file being located elsewhere does not conform to the CCI.

Differences

The compiler operation under the CCI is not changed. This is purely a coding guideline.

Migration to the CCI

Remove any option that specifies header file search paths other than the -I option (or the equivalent MPLAB X IDE

option), and use the -I option in place of this. Ensure the header file can be found in the directories specified in this

section.

3.3.5 The Number of Significant Initial Characters in an Identifier

At least the first 255 characters in an identifier (internal and external) are significant. This extends upon the

requirement of the ANSI C Standard that states a lower number of significant characters are used to identify an

object.

Example

The following example shows two poorly named variables, but names which are considered unique under the CCI.

int stateOfPortBWhenTheOperatorHasSelectedAutomaticModeAndMotorIsRunningFast;

int stateOfPortBWhenTheOperatorHasSelectedAutomaticModeAndMotorIsRunningSlow;

Differences

Former 8-bit compilers used 31 significant characters by default, but an option allowed this to be extended.

The 16- and 32-bit compilers did not impose a limit on the number of significant characters.

Migration to the CCI

No action required. You can take advantage of the less restrictive naming scheme.

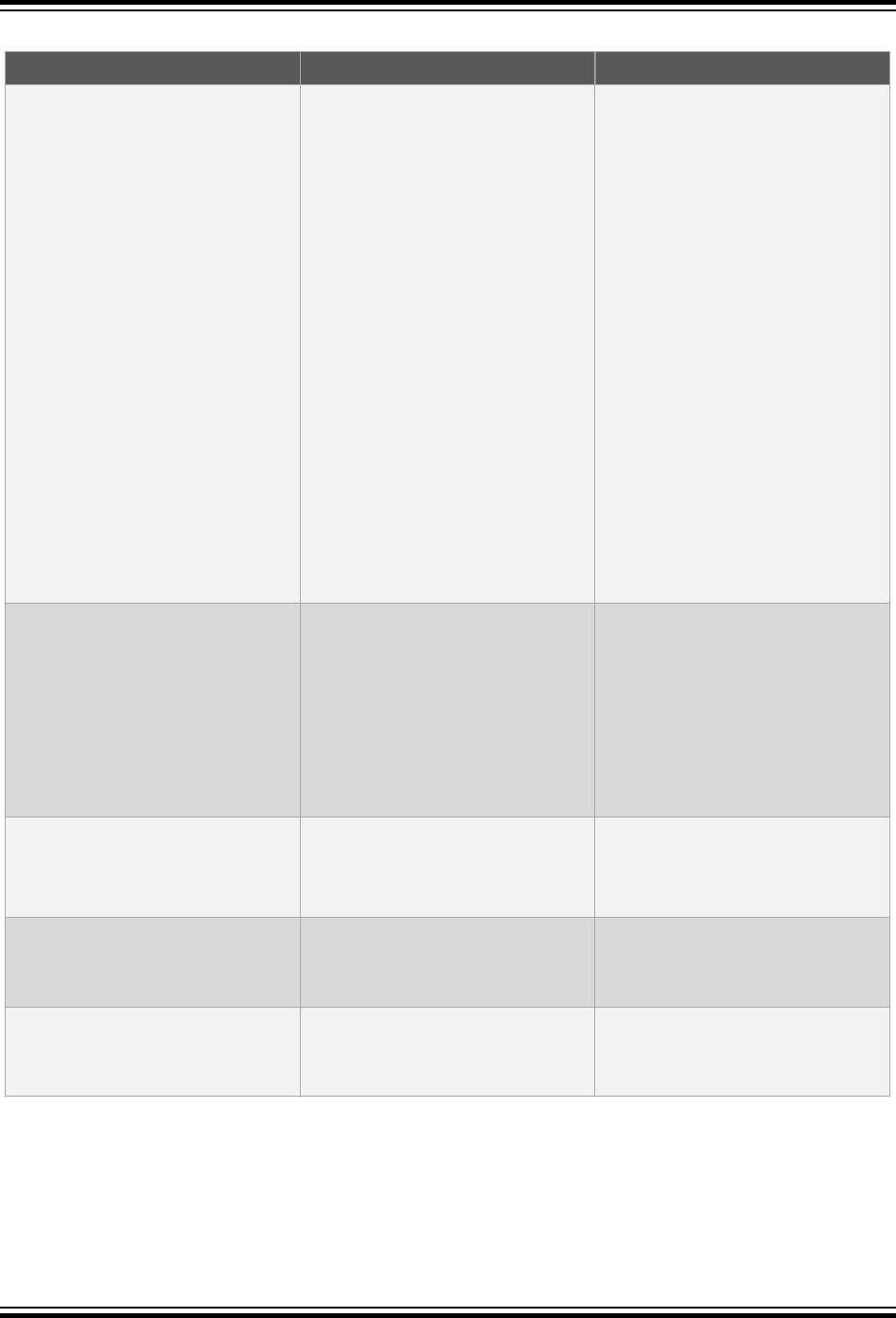

3.3.6 Sizes of Types

The sizes of the basic C types, for example char, int and long, are not fully defined by the CCI. These types, by

design, reflect the size of registers and other architectural features in the target device. They allow the device to

efficiently access objects of this type. The ANSI C Standard does, however, indicate minimum requirements for these

types, as specified in <limits.h>.

If you need fixed-size types in your project, use the types defined in <stdint.h>, for example, uint8_t or

int16_t. These types are consistently defined across all XC compilers, even outside of the CCI.

Essentially, the C language offers a choice of two groups of types: those that offer sizes and formats that are tailored

to the device you are using; or those that have a fixed size, regardless of the target.

Example

The following example shows the definition of a variable, native, whose size will allow efficient access on the target

device; and a variable, fixed, whose size is clearly indicated and remains fixed, even though it may not allow

efficient access on every device.

int native;

int16_t fixed;

Differences

This is consistent with previous types implemented by the compiler.

Migration to the CCI

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 16

If you require a C type that has a fixed size, regardless of the target device, use one of the types defined by

<stdint.h>.

3.3.7 Plain char Types

The type of a plain char is unsigned char. It is generally recommended that all definitions for the char type

explicitly state the signedness of the object.

Example

The following example

char foobar;

defines an unsigned char object called foobar.

Differences

The 8-bit compilers have always treated plain char as an unsigned type.

The 16- and 32-bit compilers used signed char as the default plain char type. The -funsigned-char option on

those compilers changed the default type to be unsigned char.

Migration to the CCI

Any definition of an object defined as a plain char and using the 16- or 32-bit compilers needs review. Any plain

char that was intended to be a signed quantity should be replaced with an explicit definition, for example.

signed char foobar;

You can use the -funsigned-char option on MPLAB XC16 and XC32 to change the type of plain char, but since

this option is not supported on MPLAB XC8, the code is not strictly conforming.

3.3.8 Signed Integer Representation

The value of a signed integer is determined by taking the two’s complement of the integer.

Example

The following shows a variable, test, that is assigned the value -28 decimal.

signed char test = 0xE4;

Differences

All compilers have represented signed integers in the way described in this section.

Migration to the CCI

No action required.

3.3.9 Integer Conversion

When converting an integer type to a signed integer of insufficient size, the original value is truncated from the most-

significant bit to accommodate the target size.

Example

The following shows an assignment of a value that is truncated.

signed char destination;

unsigned int source = 0x12FE;

destination = source;

Under the CCI, the value of destination after the alignment is -2 (that is, the bit pattern 0xFE).

Differences

All compilers have performed integer conversion in an identical fashion to that described in this section.

Migration to the CCI

No action required.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 17

3.3.10 Bitwise Operations on Signed Values

Bitwise operations on signed values act on the two’s complement representation, including the sign bit. See also

3.3.11 Right-Shifting Signed Values.

Example

The following shows an example of a negative quantity involved in a bitwise AND operation.

signed char output, input = -13;

output = input & 0x7E;

Under the CCI, the value of output after the assignment is 0x72.

Differences

All compilers have performed bitwise operations in an identical fashion to that described in this section.

Migration to the CCI

No action required.

3.3.11 Right-Shifting Signed Values

Right-shifting a signed value will involve sign extension. This will preserve the sign of the original value.

Example

The following example shows a negative quantity involved in a right-shift operation.

signed char output, input = -13;

output = input >> 3;

Under the CCI, the value of output after the assignment is -2 (that is, the bit pattern 0xFE).

Differences

All compilers have performed right-shifting as described in this section.

Migration to the CCI

No action required.

3.3.12 Conversion of Union Member Accessed Using Member with Different Type

If a union defines several members of different types and you use one member identifier to try to access the contents

of another (whether any conversion is applied to the result) is implementation-defined behavior in the standard. In the

CCI, no conversion is applied and the bytes of the union object are interpreted as an object of the type of the member

being accessed, without regard for alignment or other possible invalid conditions.

Example

The following shows an example of a union defining several members.

union {

signed char code;

unsigned int data;

float offset;

} foobar;

Code that attempts to extract offset by reading data is not guaranteed to read the correct value.

float result;

result = foobbar.data;

Differences

All compilers have not converted union members accessed via other members.

Migration to the CCI

No action required.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 18

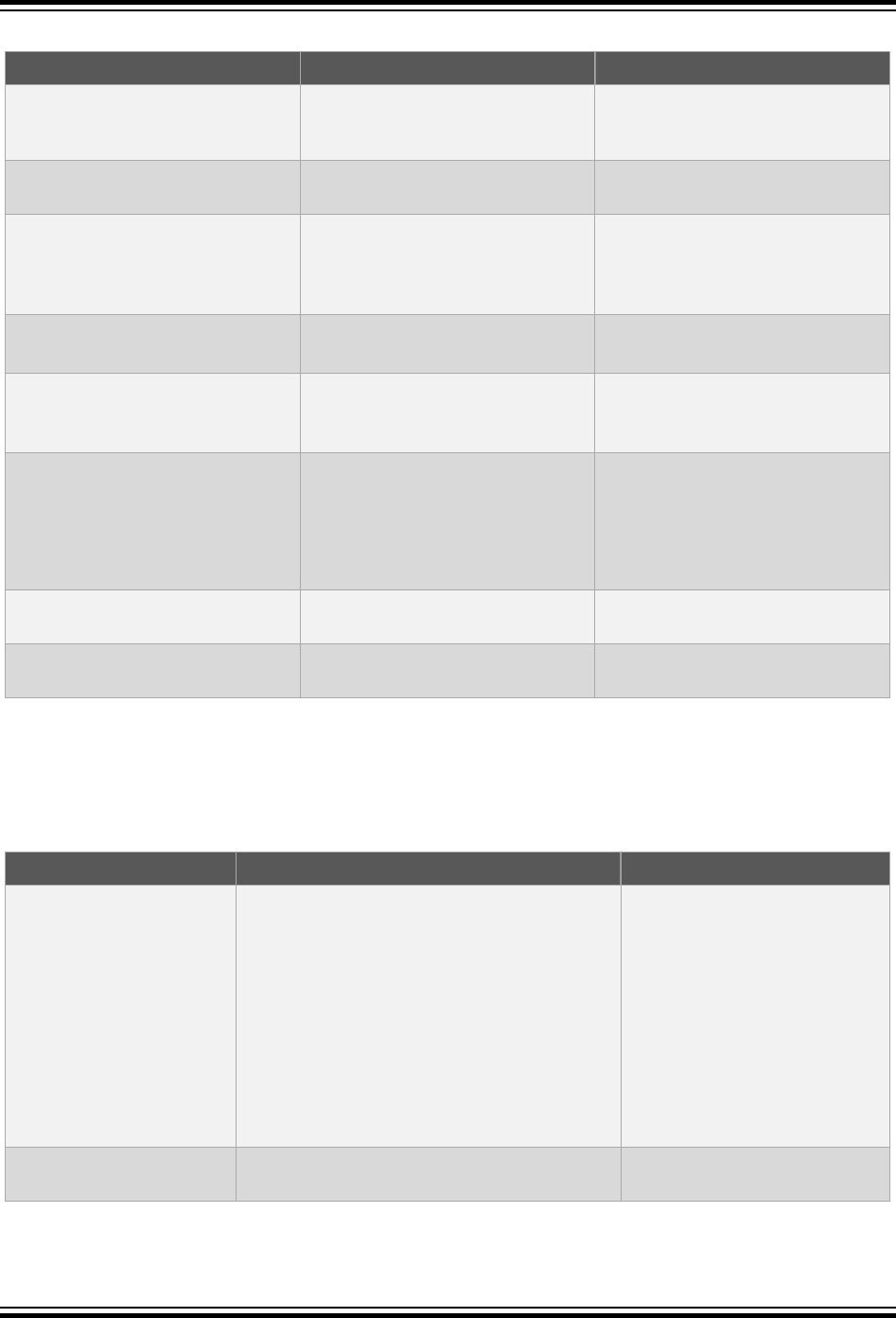

3.3.13 Default Bit-field int Type

The type of a bit-field specified as a plain int is identical to that of one defined using unsigned int. This is quite

different from other objects where the types int, signed and signed int are synonymous. It is recommended

that the signedness of the bit-field be explicitly stated in all bit-field definitions.

Example

The following shows an example of a structure tag containing bit-fields that are unsigned integers and with the size

specified.

struct OUTPUTS {

int direction :1;

int parity :3;

int value :4;

};

Differences

The 8-bit compilers have previously issued a warning if type int was used for bit-fields, but would implement the bit-

field with an unsigned int type.

The 16- and 32-bit compilers have implemented bit-fields defined using int as having a signed int type, unless

the option -funsigned-bitfields was specified.

Migration to the CCI

Any code that defines a bit-field with the plain int type should be reviewed. If the intention was for these to be

signed quantities, then the type of these should be changed to signed int. In the following example:

struct WAYPT {

int log :3;

int direction :4;

};

the bit-field type should be changed to signed int, as in:

struct WAYPT {

signed int log :3;

signed int direction :4;

};

3.3.14 Bit-Fields Straddling a Storage Unit Boundary

The standard indicates that implementations can determine whether bit-fields cross a storage unit boundary. In the

CCI, bit-fields do not straddle a storage unit boundary; a new storage unit is allocated to the structure, and padding

bits fill the gap.

Note that the size of a storage unit differs with each compiler, as this is based on the size of the base data type (for

example, int) from which the bit-field type is derived. On 8-bit compilers this unit is 8-bits in size; for 16-bit

compilers, it is 16 bits; and for 32-bit compilers, it is 32 bits in size.

Example

The following shows a structure containing bit-fields being defined.

struct {

unsigned first : 6;

unsigned second :6;

} order;

Under the CCI and using MPLAB XC8, the storage allocation unit is byte sized. The bit-field second is allocated a

new storage unit since there are only 2 bits remaining in the first storage unit in which first is allocated. The size of

this structure, order, is 2 bytes.

Differences

This allocation is identical with that used by all previous compilers.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 19

Migration to the CCI

No action required.

3.3.15 The Allocation Order of Bit-Field

The memory ordering of bit-fields into their storage unit is not specified by the ANSI C Standard. In the CCI, the first

bit defined is the least significant bit (LSb) of the storage unit in which it is allocated.

Example

The following shows a structure containing bit-fields being defined.

struct {

unsigned lo : 1;

unsigned mid :6;

unsigned hi : 1;

} foo;

The bit-field lo is assigned the least significant bit of the storage unit assigned to the structure foo. The bit-field mid

is assigned the next 6 least significant bits, and hi, the most significant bit of that same storage unit byte.

Differences

This is identical with the previous operation of all compilers.

Migration to the CCI

No action required.

3.3.16 The NULL Macro

The NULL macro is defined by <stddef.h>; however, its definition is implementation-defined behavior. Under the

CCI, the definition of NULL is the expression (0).

Example

The following shows a pointer being assigned a null pointer constant via the NULL macro.

int * ip = NULL;

The value of NULL, (0), is implicitly converted to the destination type.

Differences

The 32-bit compilers previously assigned NULL the expression ((void *)0).

Migration to the CCI

No action required.

3.3.17 Floating-Point Sizes

Under the CCI, floating-point types must not be smaller than 32 bits in size.

Example

The following shows the definition for outY, which is at least 32-bit in size.

float outY;

Differences

The 8-bit compilers have allowed the use of 24-bit float and double types.

Migration to the CCI

When using 8-bit compilers, the float and double type will automatically be made 32 bits in size once the CCI

mode is enabled. Review any source code that may have assumed a float or double type and may have been 24

bits in size.

No migration is required for other compilers.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 20

3.4 ANSI Standard Extensions

The following topics describe how the CCI provides device-specific extensions to the standard.

3.4.1 Generic Header File

A single header file <xc.h> must be used to declare all compiler- and device-specific types and SFRs. You must

include this file into every module to conform with the CCI. Some CCI definitions depend on this header being seen.

Example

The following shows this header file being included, thus allowing conformance with the CCI, as well as allowing

access to SFRs.

#include <xc.h>

Differences

Some 8-bit compilers used <htc.h> as the equivalent header. Previous versions of the 16- and 32-bit compilers

used a variety of headers to do the same job.

Migration to the CCI

Change:

#include <htc.h>

previously used in 8-bit compiler code, or family-specific header files, for example, from:

#include <p32xxxx.h>

#include <p30fxxxx.h>

#include <p33Fxxxx.h>

#include <p24Fxxxx.h>

#include "p30f6014.h"

to:

#include <xc.h>

3.4.2 Absolute Addressing

Variables and functions can be placed at an absolute address by using the __at() construct. Stack-based (auto

and parameter) variables cannot use the __at() specifier.

Example

The following shows two variables and a function being made absolute.

int scanMode __at(0x200);

const char keys[] __at(123) = { ’r’, ’s’, ’u’, ’d’};

}

Differences

The 8-bit compilers have used an @ symbol to specify an absolute address.

The 16- and 32-bit compilers have used the address attribute to specify an object’s address.

Migration to the CCI

Avoid making objects and functions absolute if possible.

In MPLAB XC8, change absolute object definitions, for example, from:

int scanMode @ 0x200;

to:

int scanMode __at(0x200);

In MPLAB XC16 and XC32, change code, for example, from:

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 21

int scanMode __attribute__((address(0x200)));

to:

int scanMode __at(0x200);

Caveats

If the __at() and __section() specifiers are both applied to an object when using MPLAB XC8, the

__section() specifier is currently ignored.

3.4.3 Far Objects and Functions

The __far qualifier can be used to indicate that variables or functions are located in ‘far memory’. Exactly what

constitutes far memory is dependent on the target device, but it is typically memory that requires more complex code

to access. Expressions involving far-qualified objects usually generate slower and larger code.

Use the native keywords discussed in the Differences section to look up information on the semantics of this qualifier.

Some devices may not have such memory implemented, in which case, use of this qualifier is ignored. Stack-based

(auto and parameter) variables cannot use the __far specifier.

Example

The following shows a variable and function qualified using __far.

__far int serialNo;

__far int ext_getCond(int selector);

Differences

The 8-bit compilers have used the qualifier far to indicate this meaning. Functions could not be qualified as far.

The 16-bit compilers have used the far attribute with both variables and functions.

The 32-bit compilers have used the far attribute with functions, only.

Migration to the CCI

For 8-bit compilers, change any occurrence of the far qualifier, for example, from:

far char template[20];

to:

__far, that is, __far char template[20];

In the 16- and 32-bit compilers, change any occurrence of the far attribute, for example, from:

void bar(void) __attribute__ ((far));

int tblIdx __attribute__ ((far));

to:

void __far bar(void);

int __far tblIdx;

Caveats

None.

3.4.4 Near Objects

The __near qualifier can be used to indicate that variables or functions are located in ‘near memory’. Exactly what

constitutes near memory is dependent on the target device, but it is typically memory that can be accessed with less

complex code. Expressions involving near-qualified objects generally are faster and result in smaller code.

Use the native keywords discussed in the Differences section to look up information on the semantics of this qualifier.

Some devices may not have such memory implemented, in which case, use of this qualifier is ignored. Stack-based

(auto and parameter) variables cannot use the __near specifier.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 22

Example

The following shows a variable and function qualified using __near.

__near int serialNo;

__near int ext_getCond(int selector);

Differences

The 8-bit compilers have used the qualifier near to indicate this meaning. Functions could not be qualified as near.

The 16-bit compilers have used the near attribute with both variables and functions.

The 32-bit compilers have used the near attribute for functions, only.

Migration to the CCI

For 8-bit compilers, change any occurrence of the near qualifier to __near, for example, from:

near char template[20];

to:

__near char template[20];

In 16- and 32-bit compilers, change any occurrence of the near attribute to __near, for example, from:

void bar(void) __attribute__ ((near));

int tblIdx __attribute__ ((near));

to

void __near bar(void);

int __near tblIdx;

Caveats

None.

3.4.5 Persistent Objects

The __persistent qualifier can be used to indicate that variables should not be cleared by the runtime startup

code.

Use the native keywords discussed in the Differences section to look up information on the semantics of this qualifier.

Example

The following shows a variable qualified using __persistent.

__persistent int serialNo;

Differences

The 8-bit compilers have used the qualifier, persistent, to indicate this meaning.

The 16- and 32-bit compilers have used the persistent attribute with variables to indicate they were not to be

cleared.

Migration to the CCI

With 8-bit compilers, change any occurrence of the persistent qualifier to __persistent, for example, from:

persistent char template[20];

to:

__persistent char template[20];

For the 16- and 32-bit compilers, change any occurrence of the persistent attribute to __persistent, for

example, from:

int tblIdx __attribute__ ((persistent));

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 23

to

int __persistent tblIdx;

Caveats

None.

3.4.6 X and Y Data Objects

The __xdata and __ydata qualifiers can be used to indicate that variables are located in special memory regions.

Exactly what constitutes X and Y memory is dependent on the target device, but it is typically memory that can be

accessed independently on separate buses. Such memory is often required for some DSP instructions.

Use the native keywords discussed in the Differences section to look up information on the semantics of these

qualifiers.

Some devices may not have such memory implemented; in which case, use of these qualifiers is ignored.

Example

The following shows a variable qualified using __xdata, as well as another variable qualified with __ydata.

__xdata char data[16];

__ydata char coeffs[4];

Differences

The 16-bit compilers have used the xmemory and ymemory space attribute with variables.

Equivalent specifiers have never been defined for any other compiler.

Migration to the CCI

For 16-bit compilers, change any occurrence of the space attributes xmemory or ymemory to __xdata, or __ydata

respectively, for example, from:

char __attribute__((space(xmemory)))template[20];

to:

__xdata char template[20];

Caveats

None.

3.4.7 Banked Data Objects

The __bank(num) qualifier can be used to indicate that variables are located in a particular data memory bank. The

number, num, represents the bank number. Exactly what constitutes banked memory is dependent on the target

device, but it is typically a subdivision of data memory to allow for assembly instructions with a limited address width

field.

Use the native keywords discussed in the Differences section to look up information on the semantics of these

qualifiers.

Some devices may not have banked data memory implemented, in which case, use of this qualifier is ignored. The

number of data banks implemented will vary from one device to another.

Example

The following shows a variable qualified using __bank().

__bank(0) char start;

__bank(5) char stop;

Differences

The 8-bit compilers have used the four qualifiers bank0, bank1, bank2 and bank3 to indicate the same, albeit more

limited, memory placement.

XC32 Compiler for PIC32M

Common C Interface

© 2020 Microchip Technology Inc.

User Guide

DS50002799B-page 24

Equivalent specifiers have never been defined for any other compiler.

Migration to the CCI

For 8-bit compilers, change any occurrence of the bankx qualifiers to __bank(), for example, from:

bank2 int logEntry;

to:

__bank(2) int logEntry;

Caveats

This feature is not yet implemented in MPLAB XC8.

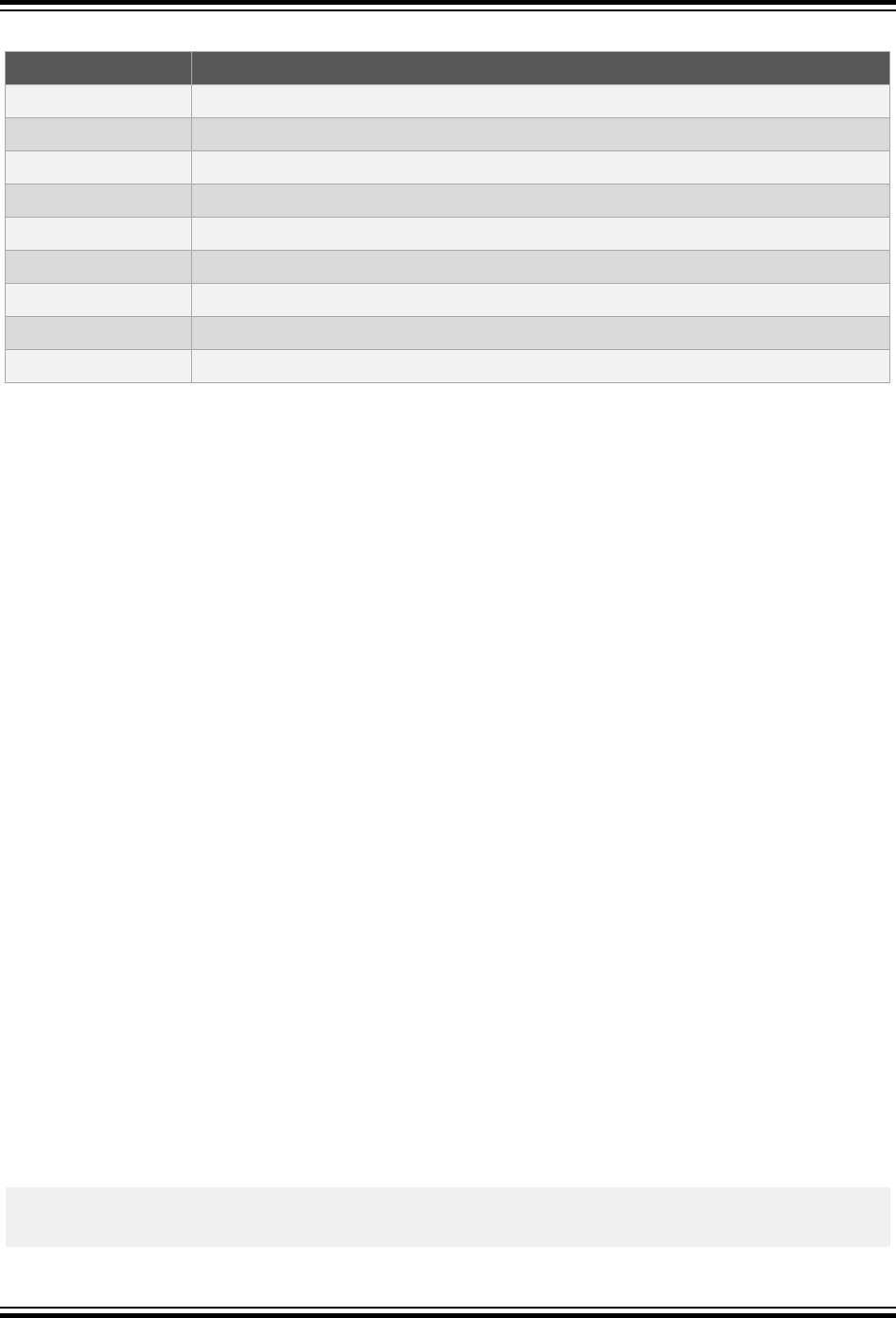

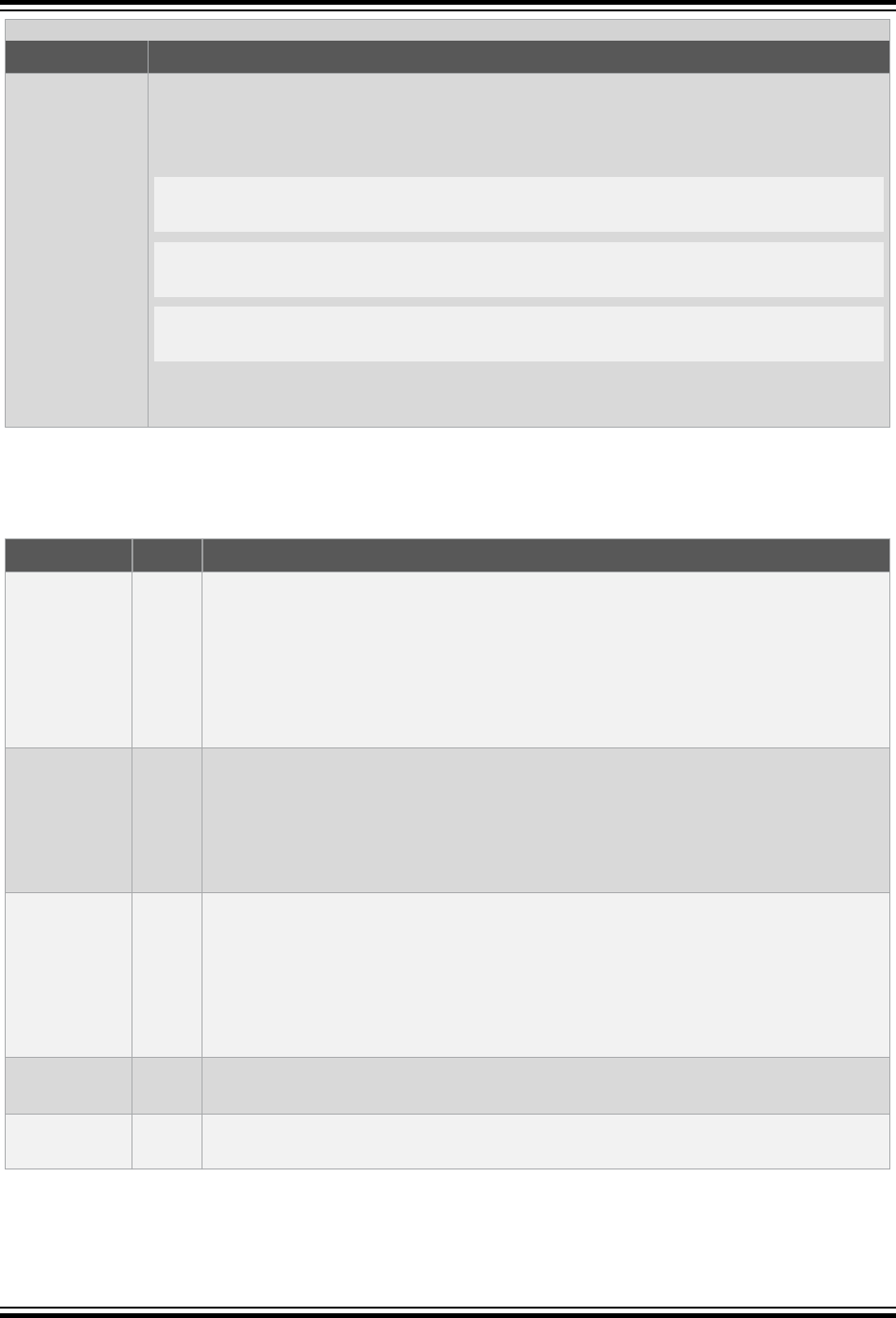

3.4.8 Alignment of Objects

The __align(alignment) specifier can be used to indicate that variables must be aligned on a memory address

that is a multiple of the alignment specified. The alignment term must be a power of 2. Positive values request that

the object’s start address be aligned.

Use the native keywords discussed in the Differences section to look up information on the semantics of this

specifier.

Example

The following shows variables qualified using __align() to ensure they start on an address that is a multiple of 2.

__align(2) char coeffs[6];

Differences

An alignment feature has never been implemented on 8-bit compilers.

The 16- and 32-bit compilers used the aligned attribute with variables.

Migration to the CCI

For 16- and 32-bit compilers, change any occurrence of the aligned attribute to __align, for example, from: